Computer Architecture

Chapter 4 Problems:

- 1. Vahid 4.8

- 2. Vahid 4.11

- 3. Vahid 4.13

- 4. In class we used the design procedure to design a Full Adder (FA)

and a magnitude comparator cell. Use the design procedure to design a

cell circuit that only does A greater than B. The cell uses a

ripple-carry like operation for larger word lengths similar to the FA.

Create a truth table, write optimized SOP or POS equations (we will

cover how to do this in chapter 6), draw the cell, and draw a circuit

using the cell for a 4-bit A greater than B comparator.

- 5. Design a 3x3 multiplier circuit using Full Adders (minimize the

number of FAs) and the minimum amount of additional combinational

logic.

- 6. Using Full Adders, comparators, multiplexers, decoders, and the

minimum amount of additional logic, design a cell for an ALU that can

perform addition, A greater than B comparison, logical AND, or logical

OR. The operation is determined by two select lines. You may use

multiplexers and the minimum amount of additional combinational

logic.

- 7. Use the design process where needed and design a Binary Coded

Decimal (BCD) adder. The circuit has a carry in, carry out, an A input,

a B input, and an S output. The A, B, and S signals are each 4 bits.

As the designer, you need to take into account errors on the input.

Describe what you decided to handle the error.

A BCD number is a 4-bit number where the only valid combination of bits

represent decimal numbers 0 through 9. Any other combination greater

than 9 is considered invalid. When adding two BCD numbers where the

result is greater than 9, the intermediate result must have 6 added

to it to create the correct BCD output and a carry out.

Use Full Adders and the minimum amount of additional combinational

logic.

- 8. Design a circuit using multipliers and adders to implement the

following arithmetic equation:

F = A + B * C

Where A is a 5 bit bus, B and C are 7 bit buses.

Draw a schematic showing the number of required bits in each bus and

any intermediate bus.

- 9. A common operation in graphics is multiplying a 4 component

vertex with a 4x4 matrix to create a transformed vertex. Create a

circuit using a hierarchical method to implement this. The

hierarchical method is a common way of abstracting away the

details of implementation. We did this in class by creating a 4-bit

adder using Full Adders and a Full Adder using basic logic gates.

Draw circuits of repeatable components in your design. You may

use multipliers and adders as components. You do not need to show

the number of bits in a bus.

- 10. Design a variable length shift register with the following design

goals:

- A. The length can vary from 3 to 5.

- B. The change in length is synchronous to the clock.

- C. The bit depth of the shift register is one bit

(design the circuit to handle one bit in and one bit out.)

- D. Use D-type flip-flops and the minimum amount of

combinational logic necessary.

- E. The register has a mode where the output is a 0.

- 11. Design a 4-bit multi-function register, with left and right

serial inputs, and parallel outputs that has the following functions:

Mode Control

S1 S0 |

Register Operation |

| 0 0 |

Add Three |

| 0 1 |

Shift Left |

| 1 0 |

Complement |

| 1 1 |

Shift Right |

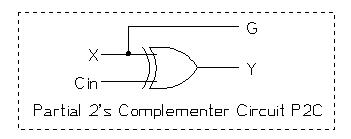

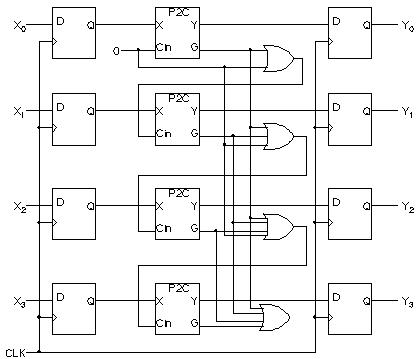

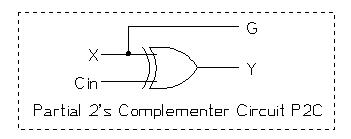

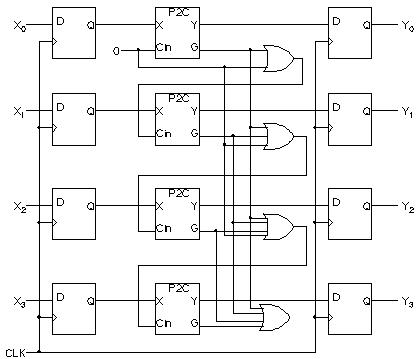

- 12. The following sequential circuit has a 4 bit bus, X, going into a

bank of 4 D-type flip-flops. The output of the flip-flops are connected

to the inputs of a 4 bit 2's complementer circuit with carry lookahead.

The 4 output bits of the 2's complementer are connected to a bank of

4 D-type flip-flops. All of the flip-flops share a common clock signal.

What is the maximum clock frequency of this circuit? The flip-flop setup

time is 8 nS, hold time is 2 nS, and propagation delay is 4 nS. The

propagation delay of the XOR gate is 4 nS and OR gates have a

propagation delay of 3 nS?

- 13. Using two 4-bit binary counters, design an 8 bit counter. The

4-bit counter has a count enable input, CE, and a terminal count, TC,

that is 1 when the counter reaches 15.

- 14. Using 4-bit binary counters with parallel load,

design a circuit that counts from 8 up to 38 and repeats.