Computer Architecture

Section 4 Problems:

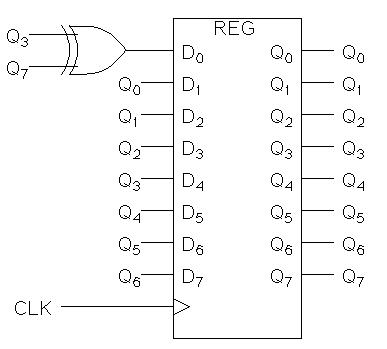

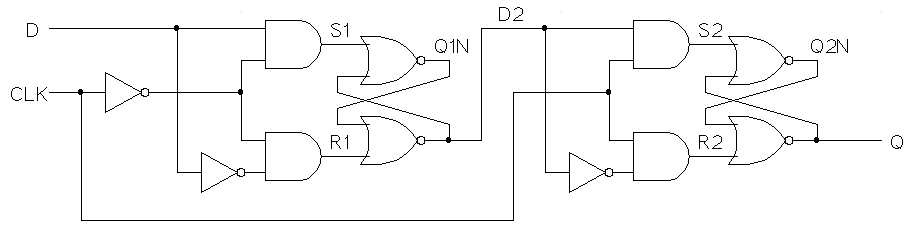

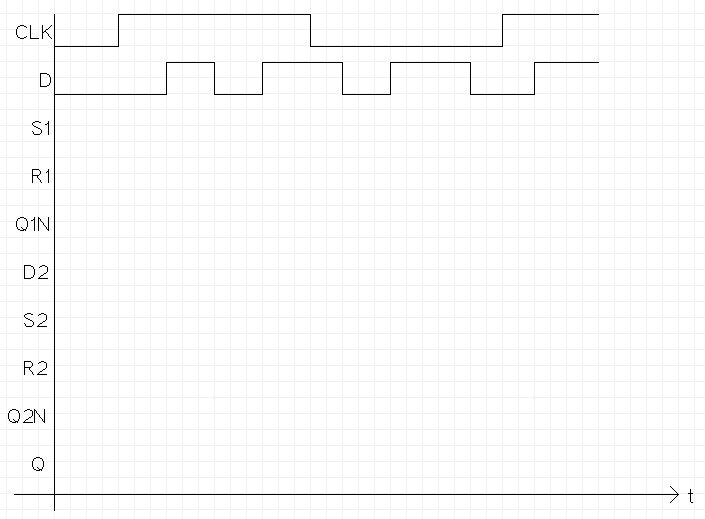

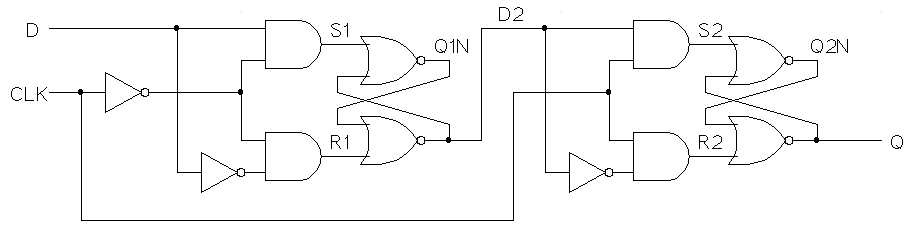

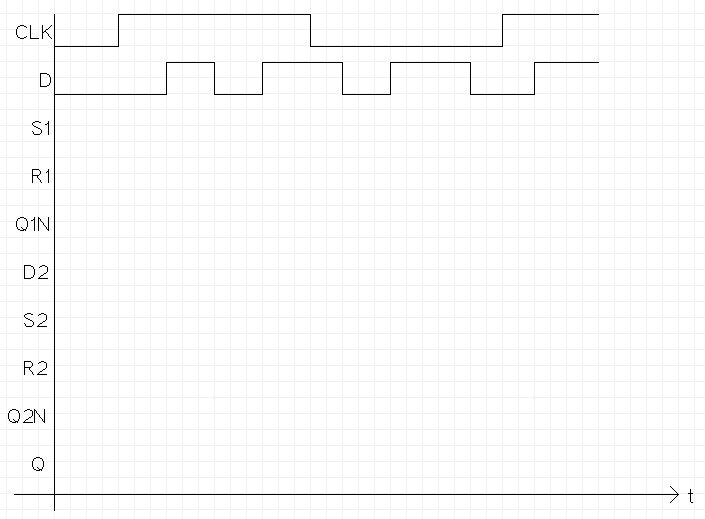

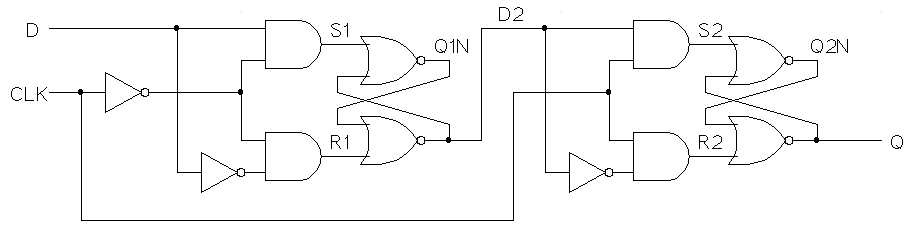

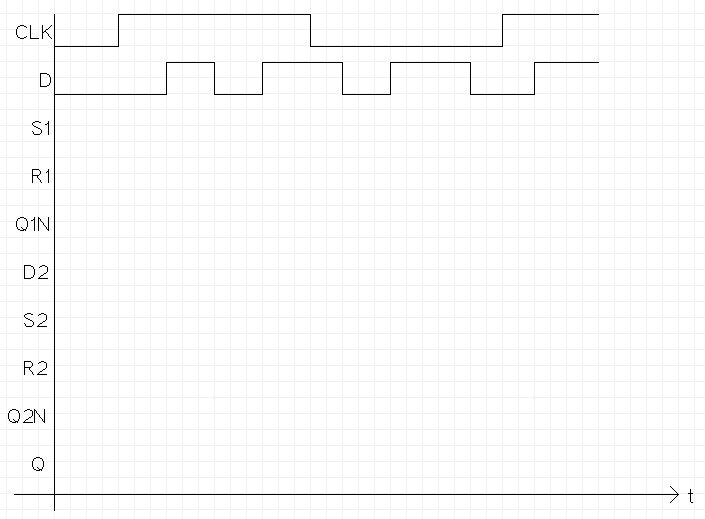

- 1. The D type flip-flop shown below is made of D type latches. Finish

the timing diagram for the given input signals.

- 2. In class and the book we used NOR gates to build a latch. Design

a level sensitive SR latch using NAND gates.

- 3. Use the design process to design a Mealy model circuit that detects

the bit pattern 1110101 (least significant bit first). The pattern can

overlap. The output detection signal goes high when the pattern is

detected, 0 otherwise. Show a state diagram and state table.

- 4. Using the design process, design a 4-bit counter. There are no input

signals and the only output signals are the current state signals.

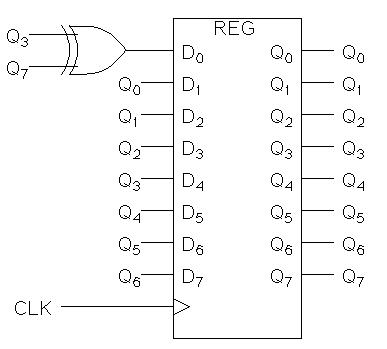

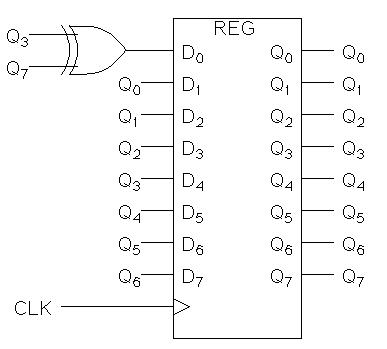

- 5. For the circuit given below, determine the output, Q,

for 12 clock cycles starting with Q = 00110111.