## **Digital IC Design and Architecture**

# Combinational Logic and Circuits

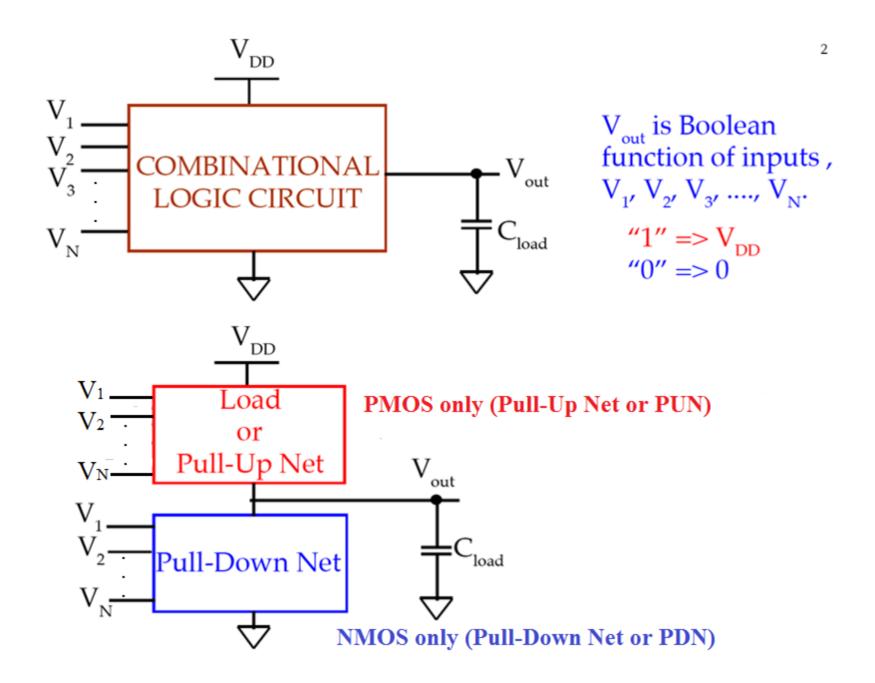

## Static CMOS Circuit

- At every point in time (except during the switching transients) each gate output is connected to either  $V_{DD}$  or  $V_{ss}$  via a low-resistive path.

- The outputs of the gates assume at all times the value of the Boolean function, implemented by the circuit (ignoring, once again, the transient effects during switching periods).

- This is in contrast to the dynamic circuit class, which relies on temporary storage of signal values on the capacitance of high impedance circuit nodes.

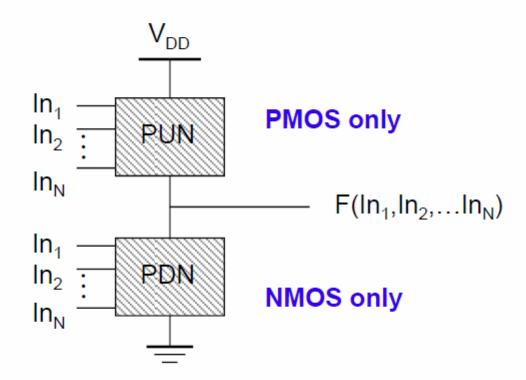

## **Static Complementary CMOS**

- PUN and PDN are dual logic networks

- PUN and PDN functions are complementary

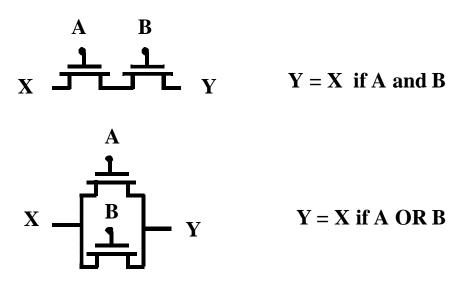

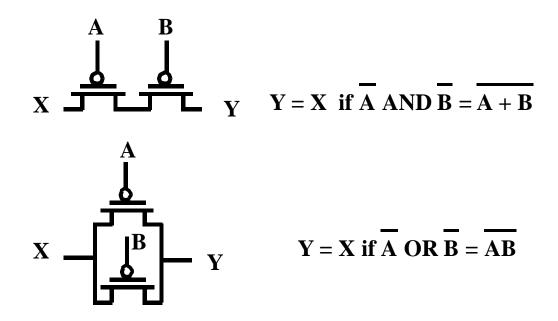

### NMOS Transistors in Series/Parallel Connection

Transistors can be thought as a switch controlled by its gate signal NMOS switch closes when switch control input is high

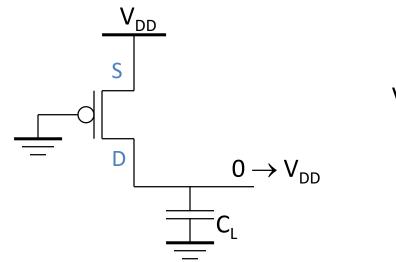

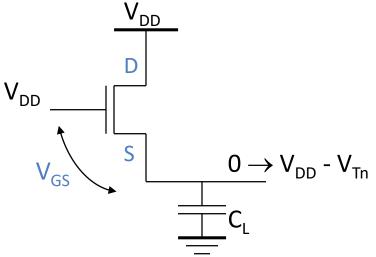

NMOS Transistors pass a "strong" 0 but a "weak" 1

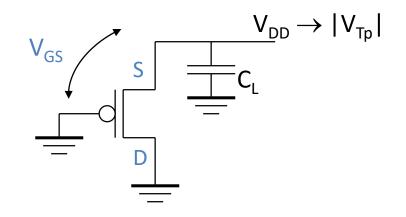

### PMOS Transistors in Series/Parallel Connection PMOS switch closes when switch control input is low

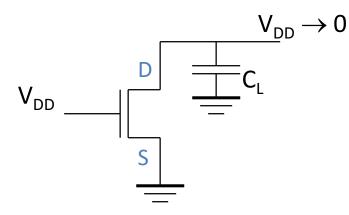

PMOS Transistors pass a "strong" 1 but a "weak" 0

## **Threshold Drops**

PUN – Pull Up Network

PDN – Pull Down Network

## **Complementary CMOS Logic Style**

PUP is the <u>DUAL</u> of PDN

(can be shown using DeMorgan's Theorem's)

$$\overline{\overline{A} + B} = \overline{\overline{A}}\overline{\overline{B}}$$

$$\overline{\overline{A}}\overline{\overline{B}} = \overline{\overline{A}} + \overline{\overline{B}}$$

• The complementary gate is inverting

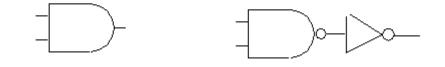

AND = NAND + INV

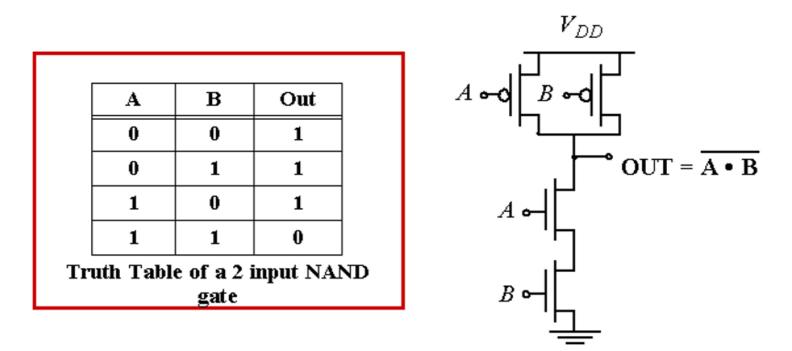

### **Example Gate: NAND**

PDN: G = A B  $\Rightarrow$  Conduction to GND PUN: F =  $\overline{A} + \overline{B} = \overline{AB} \Rightarrow$  Conduction to V<sub>DD</sub>  $\overline{G(In_1, In_2, In_3, ...)} \equiv F(\overline{In_1}, \overline{In_2}, \overline{In_3}, ...)$

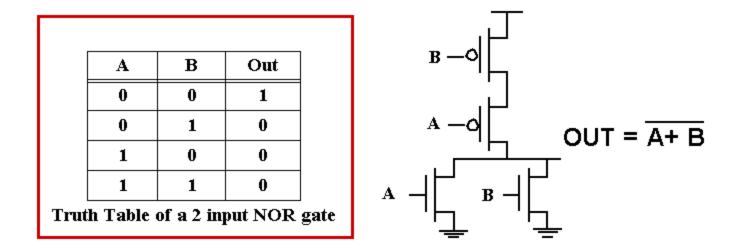

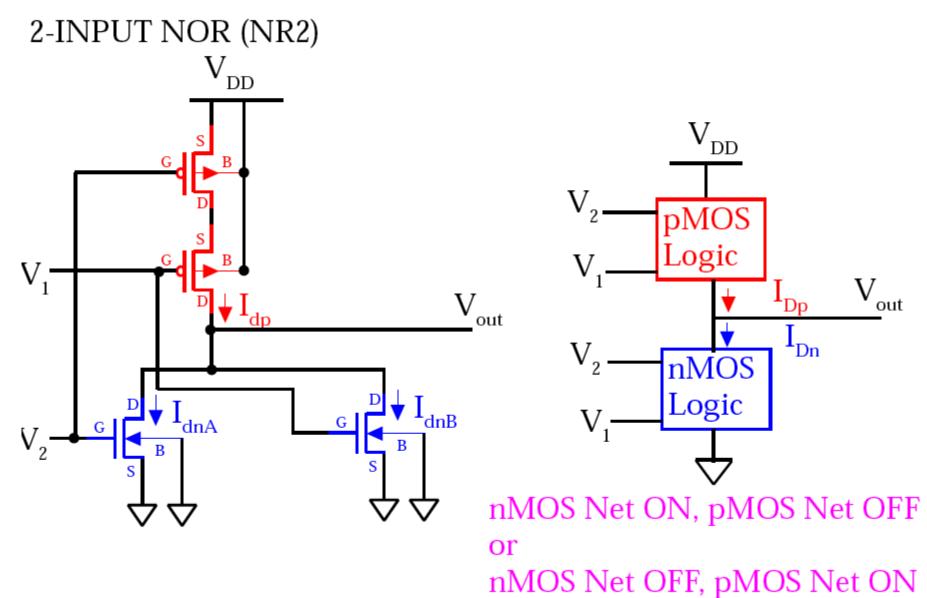

### **Example Gate: NOR**

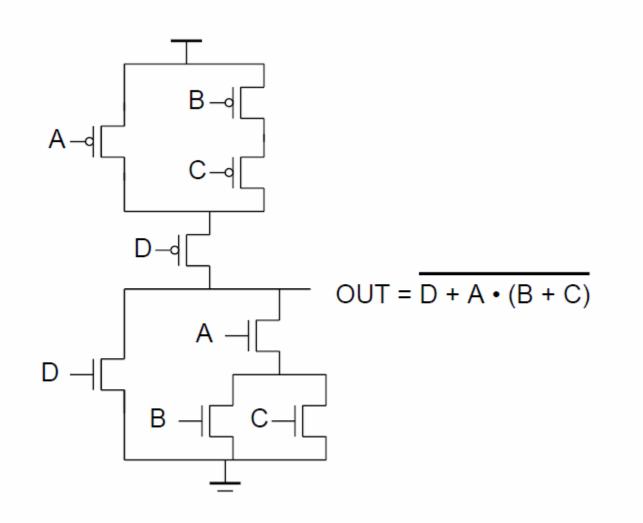

### Complex CMOS Gate

## **Digital IC Design and Architecture**

# Combinational Logic: CMOS Implementation

#### **CMOS LOGIC GATES**

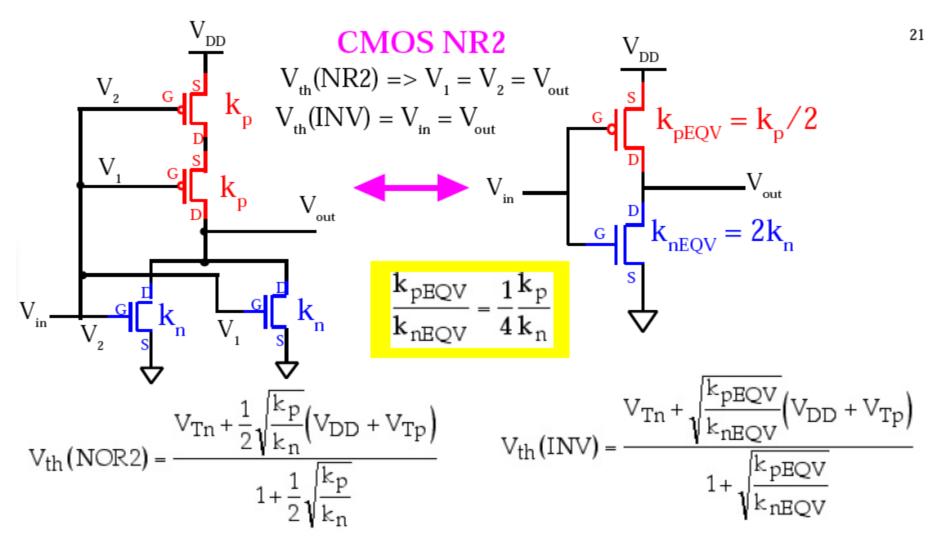

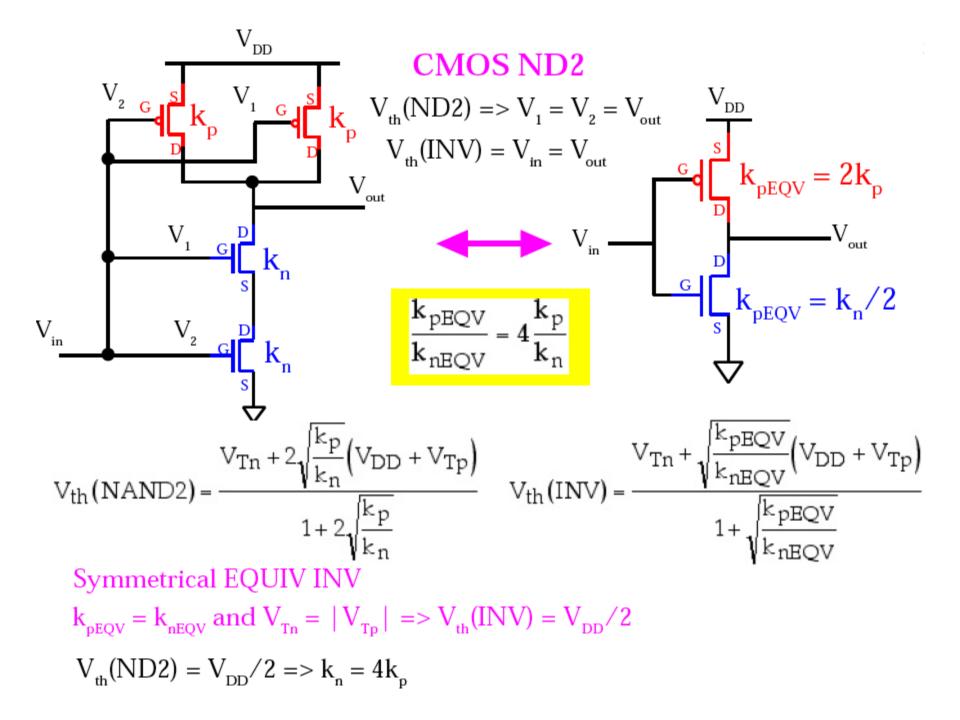

Symmetrical EQUIV INV

$\begin{aligned} k_{pEQV} &= k_{nEQV} \text{ or } k_{pEQV} / k_{nEQV} = 1 \text{ and } V_{Tn} = |V_{Tp}| => V_{th}(INV) = V_{DD}/2 \\ V_{th}(NR2) &= V_{DD}/2 => k_p = 4k_n \end{aligned}$

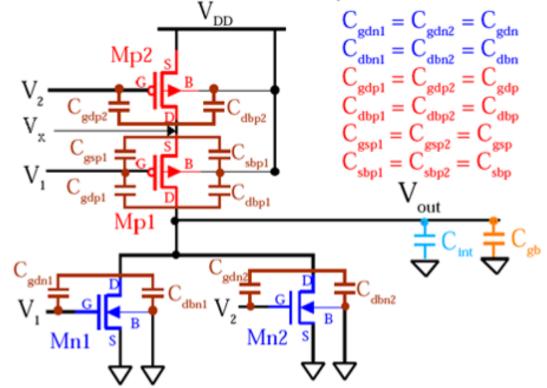

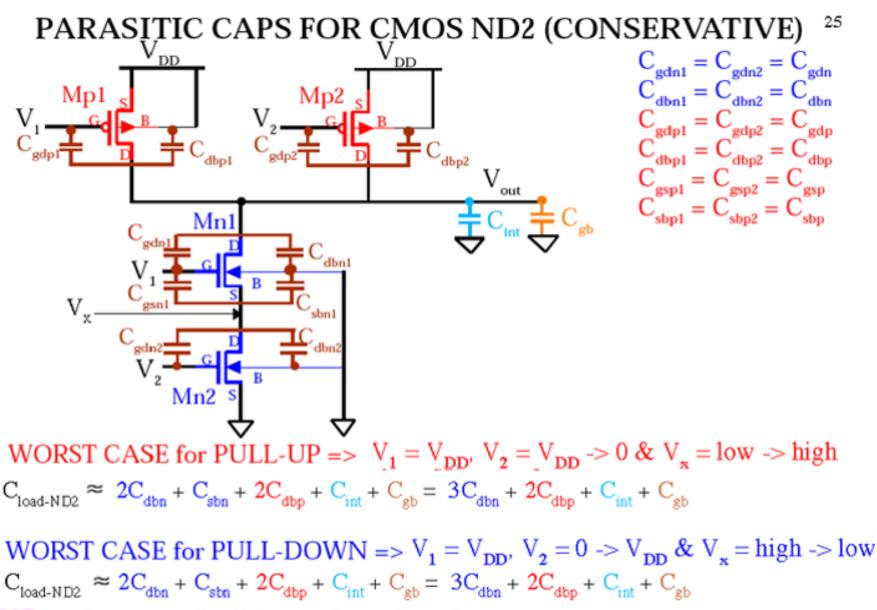

#### PARASITIC CAPS FOR CMOS NR2 (CONSERVATIVE)

WORST CASE for PULL-UP =>  $V_1 = 0$ ,  $V_2 = V_{DD} \rightarrow 0$  &  $V_x = low \rightarrow high C_{load-NR2} \approx 2C_{dbn} + 2C_{dbp} + C_{sbp} + C_{int} + C_{gb} = 2C_{dbn} + 3C_{dbp} + C_{int} + C_{gb}$

WORST CASE for PULL-DOWN =>  $V_1 = 0$ ,  $V_2 = 0 -> V_{DD}$  &  $V_x = high -> low$   $C_{load-NR2} \approx 2C_{dbn} + 2C_{dbp} + C_{sbp} + C_{int} + C_{gb} = 2C_{dbn} + 3C_{dbp} + C_{int} + C_{gb}$ NRn:  $C_{load-NRn} \approx nC_{dbn} + (2n-1)C_{dbp} + C_{int} + C_{gb}$

22

#### CMOS NR DESIGN STRATEGIES

#### NR2:

#### 1. Symmetric Inverter $V_{th} = V_{DD}/2$ : $V_{th}(NR2) = V_{DD}/2 => k_p = 4k_n$

### 2. Propogation delay $\tau_{\text{PHL}}$ or $\tau_{\text{PLH}}$ : $\tau_{\text{PHL-NR2}} \approx \frac{C_{\text{load}-\text{NR2}}}{2\text{kn}(\text{VDD-VT0n})} \left[ \frac{2V_{\text{T0n}}}{V_{\text{DD}} - V_{\text{T0n}}} + \ln\left(\frac{4(V_{\text{DD}} - V_{\text{T0n}})}{V_{\text{DD}}} - 1\right) \right]$ $\tau_{\text{PLH-NR2}} \approx \frac{C_{\text{load}-\text{NR2}}}{\frac{kp}{2}} \left[ \frac{2|V_{\text{T0p}}|}{V_{\text{DD}} - |V_{\text{T0p}}|} + \ln\left(\frac{4(V_{\text{DD}} - |V_{\text{T0p}}|)}{V_{\text{DD}}} - 1\right) \right]$ NRn:

### 1. Symmetric Inverter $V_{th} = V_{DD}/2$ : $V_{th}(NRn) = V_{DD}/2 => k_p = n^2 k_n$ 2. Propogation delay $\tau_{PHL}$ or $\tau_{PLH}$ : $\tau_{PHL-NRn} \approx \frac{C_{load-NRn}}{nkn(VDD-VT0n)} \left[ \frac{2V_{T0n}}{V_{DD} - V_{T0n}} + ln \left( \frac{4(V_{DD} - V_{T0n})}{V_{DD}} - 1 \right) \right]$ $\tau_{PLH-NRn} \approx \frac{C_{load-NRn}}{kp(VDD-|VT0p|)} \left[ \frac{2|V_{T0p}|}{V_{DD} - |V_{T0p}|} + ln \left( \frac{4(V_{DD} - |V_{T0p}|)}{V_{DD}} - 1 \right) \right]$

**NDn:**  $C_{load-NDn} \approx (2n-1)C_{dbn} + nC_{dbp} + C_{int} + C_{gb}$

#### **CMOS ND DESIGN STRATEGIES**

### ND2: 1. Symmetric Inverter $V_{th} = V_{DD}/2$ : $V_{th}(ND2) = V_{DD}/2 => k_n = 4k_p$ 2. Propogation delay $\tau_{PHL}$ or $\tau_{PLH}$ : $\tau_{PHL-ND2} \approx \frac{C_{load-ND2}}{\frac{kn}{2}} \left[ \frac{2V_{T0n}}{V_{DD}-V_{T0n}} + \ln\left(\frac{4(V_{DD}-V_{T0n})}{V_{DD}}-1\right) \right]$ $\tau_{PLH-ND2} \approx \frac{C_{load-ND2}}{2kp(VDD-|VT0p|)} \left[ \frac{2|V_{T0p}|}{V_{DD}-|V_{T0p}|} + \ln\left(\frac{4(V_{DD}-|V_{T0p}|)}{V_{DD}}-1\right) \right]$ NDn:

1. Symmetric Inverter  $V_{th} = V_{DD}/2$ :  $V_{th}(NDn) = V_{DD}/2 => k_n = n^2 k_p$

2. Propogation delay  $\tau_{PHL}$  or  $\tau_{PLH}$ :

$$\begin{aligned} \tau_{\text{PHL-NDn}} &\approx \frac{C_{\text{load}-\text{NDn}}}{\frac{kn(\text{VDD-VT0n})}{n}} \left[ \frac{2V_{\text{T0n}}}{V_{\text{DD}} - V_{\text{T0n}}} + \ln\left(\frac{4(V_{\text{DD}} - V_{\text{T0n}})}{V_{\text{DD}}} - 1\right) \right] \\ \tau_{\text{PLH-NDn}} &\approx \frac{C_{\text{load}-\text{NDn}}}{nkp(\text{VDD-|VT0p})} \left[ \frac{2|V_{\text{T0p}}|}{V_{\text{DD}} - |V_{\text{T0p}}|} + \ln\left(\frac{4(V_{\text{DD}} - |V_{\text{T0p}}|)}{V_{\text{DD}}} - 1\right) \right] \end{aligned}$$

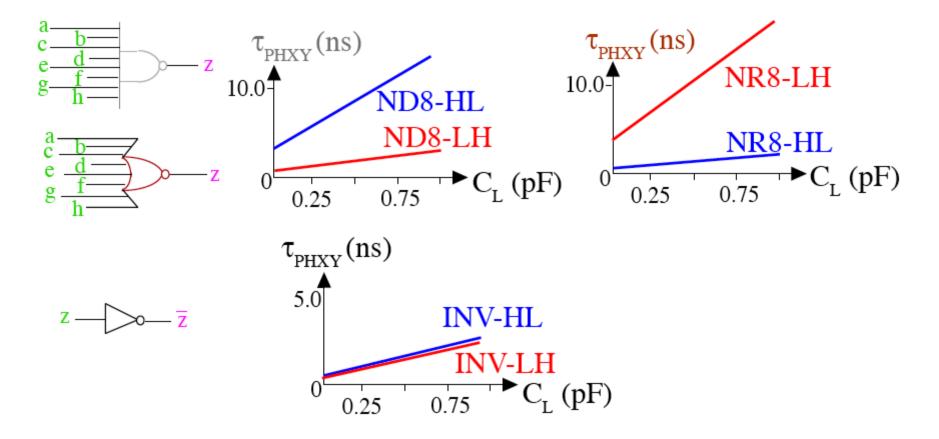

#### TYPICAL CMOS NAND AND NOR DELAYS Delays for a Family of NAND & NOR gates

- 1.  $W_n = 6.4 \ \mu m$ ,  $L_n = 1 \ \mu m$ , and  $W_p = 12.8 \ \mu m$ ,  $L_p = 1 \ \mu m$ .

- 2.  $t_{input-rise/fall} = 0.1 \text{ ns}$  and  $C_{load} = 0 \rightarrow 1 \text{ pF}.$

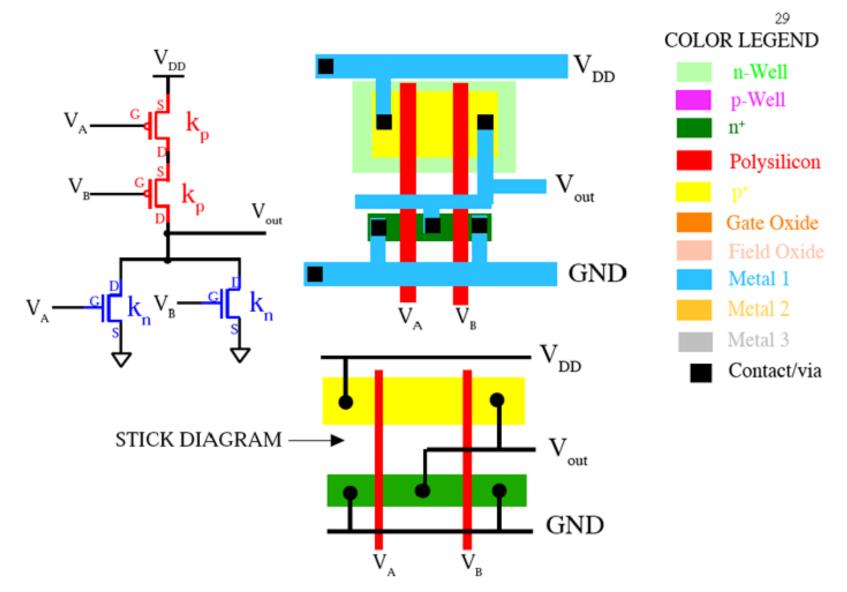

## NR2 Layout Example

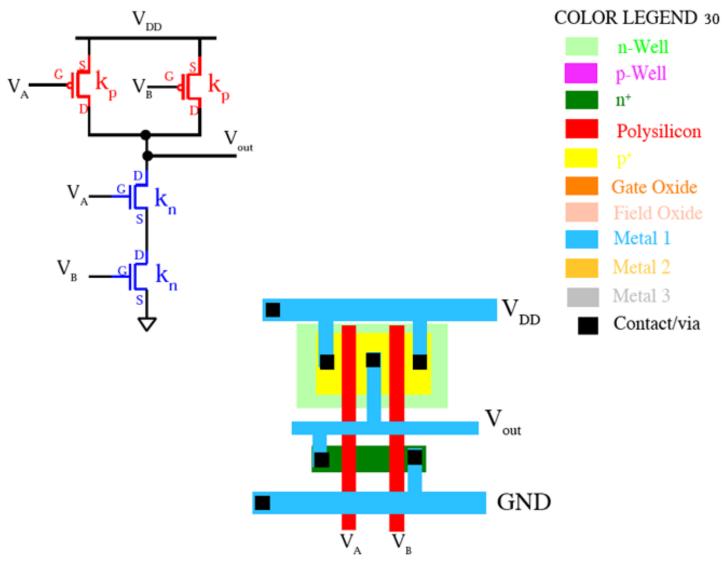

## ND2 Layout Example

· · · · · ·

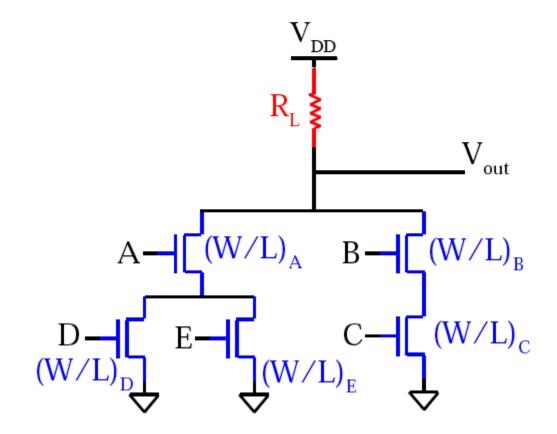

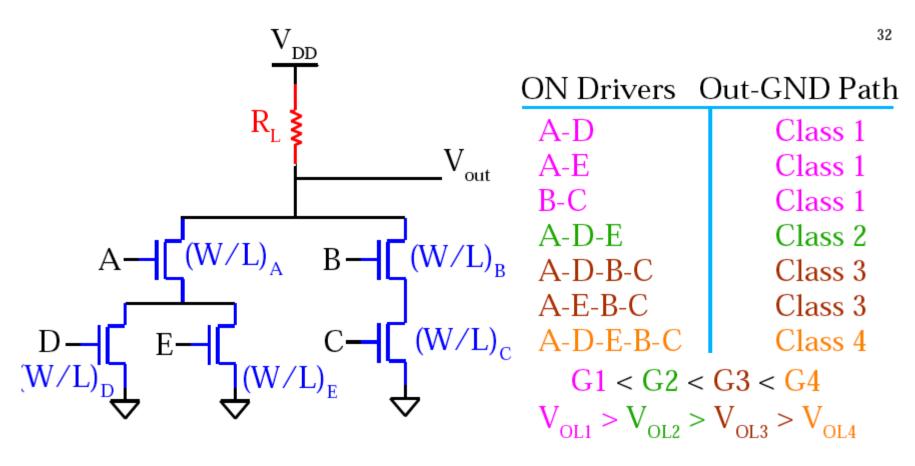

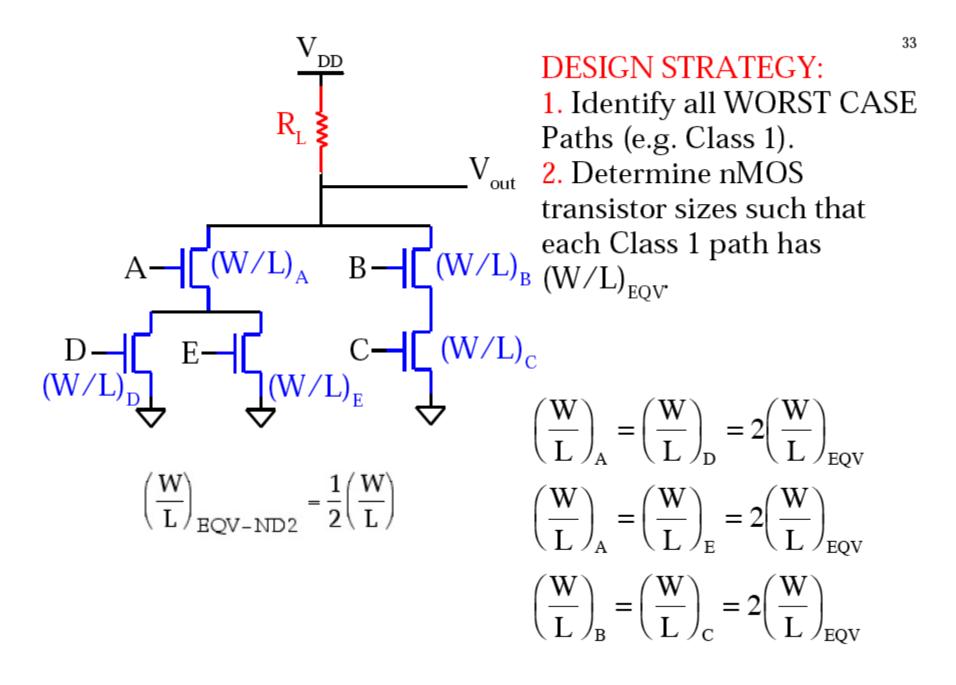

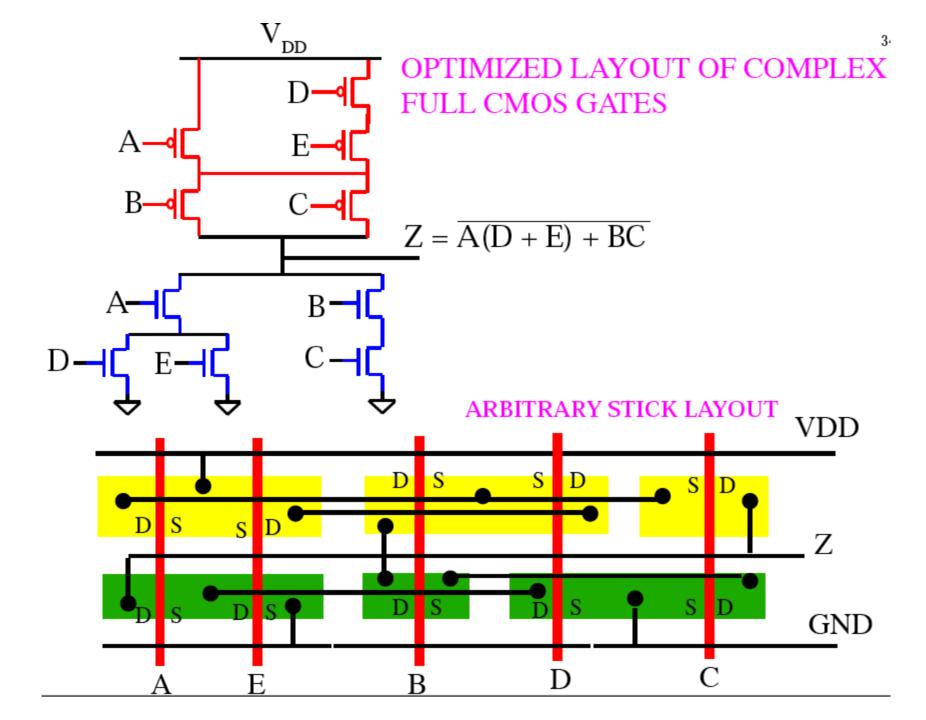

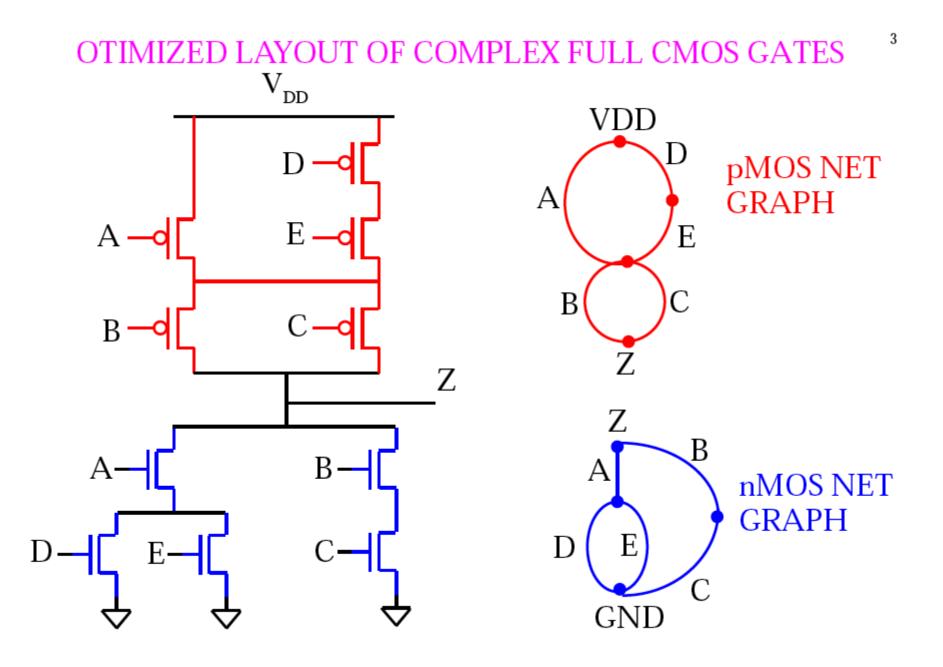

COMPLEX LOGIC GATES

$$Z = \overline{A(D + E) + BC}$$

"OR" OPS PERFORMED BY PARALLEL CONECTED DRIVERS. "AND" OPS PERFORMED BY SERIES CONNECTED DRIVERS. "INVERSION" IS PROVIDED BY NATURE OF MOS CIRCUIT OP.

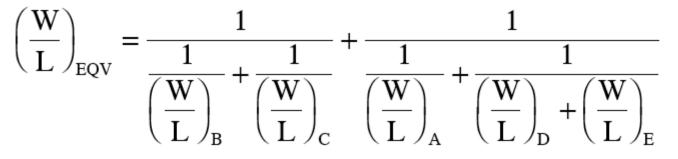

EQV INVERTER (for case G4 where A = B = C = D = E = 1)

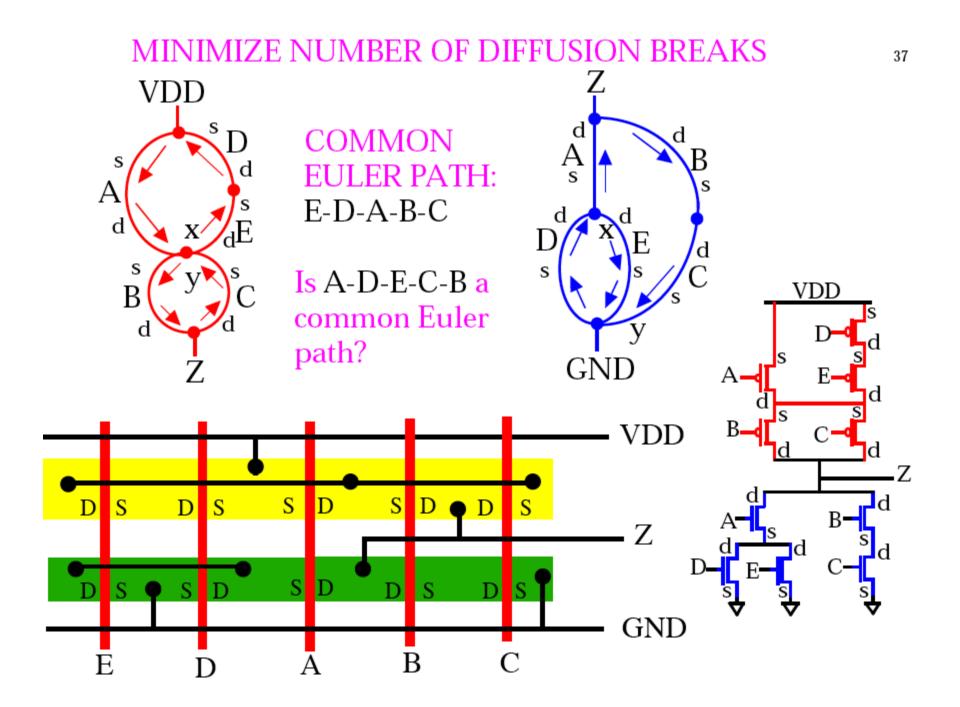

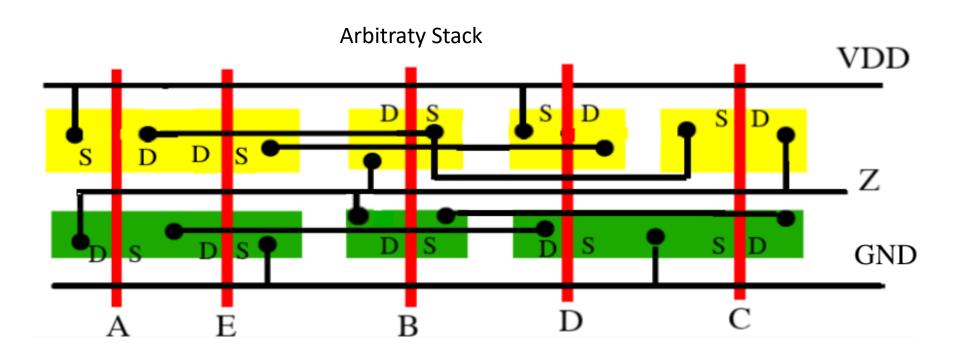

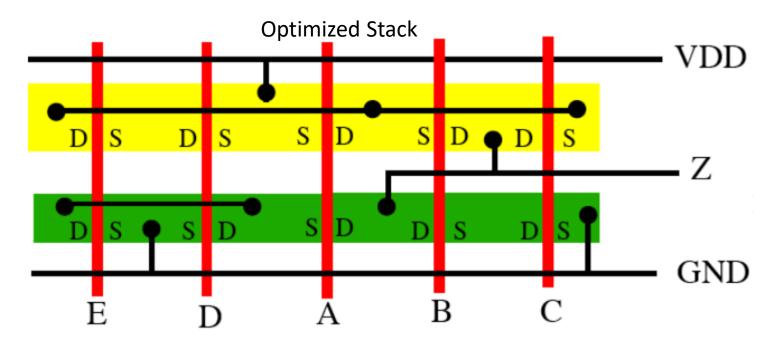

#### ALGORYTHYM FOR LINE OF GATES LAYOUT STYLE

- 1. Find all Euler paths that cover the graph.

- 2. Find common n- and p- Euler paths.

- 3. If no Euler paths are found in step 2, break the gate in the minimum number of places that to achieve step 2 with separate common Euler paths.

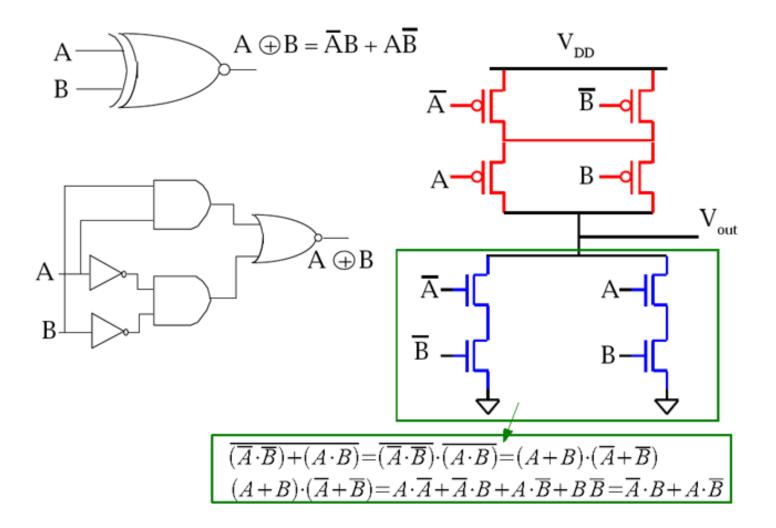

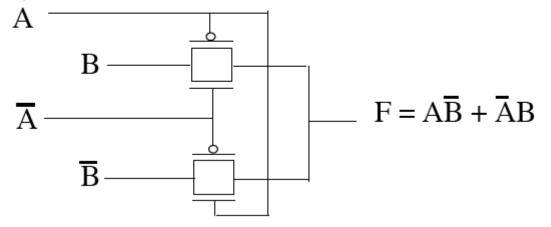

#### FULL CMOS XOR GATE

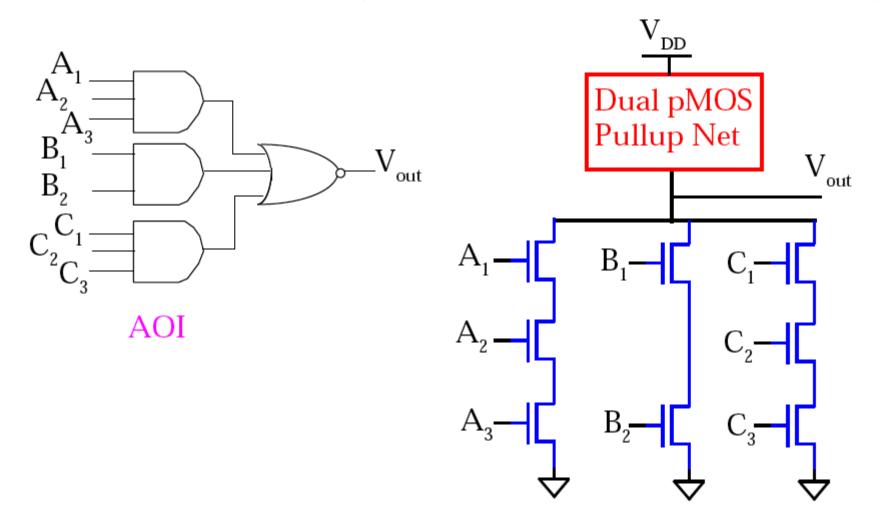

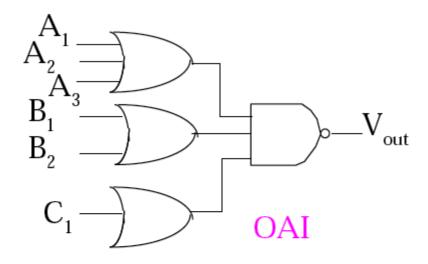

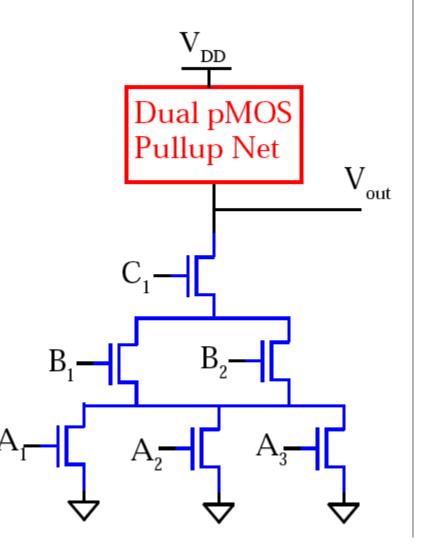

#### **AOI & OAI GATES**

AOI -> AND-OR-INVERT (for SUM - of - PRODUCTS Realization) OAI -> OR-AND-INVERT (for PRODUCT - of - SUMS Realization)

OAI -> OR-AND-INVERT (for PRODUCT - of - SUMS Realization)

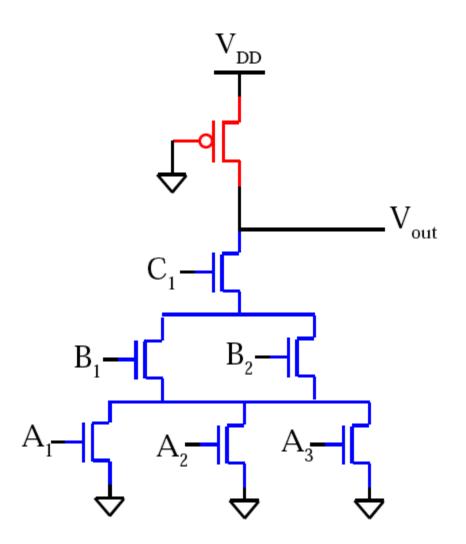

#### Pseudo-nMOS OAI Realization

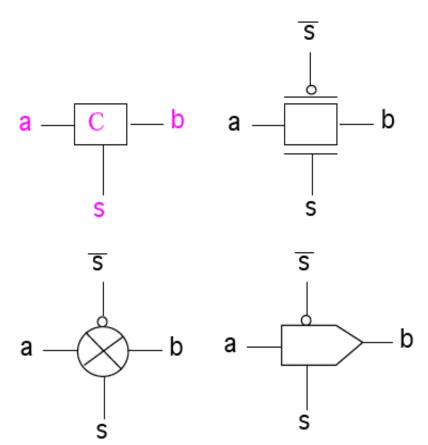

#### CMOS Transmission Gates (TGs) & TG Logic

SYMBOLS

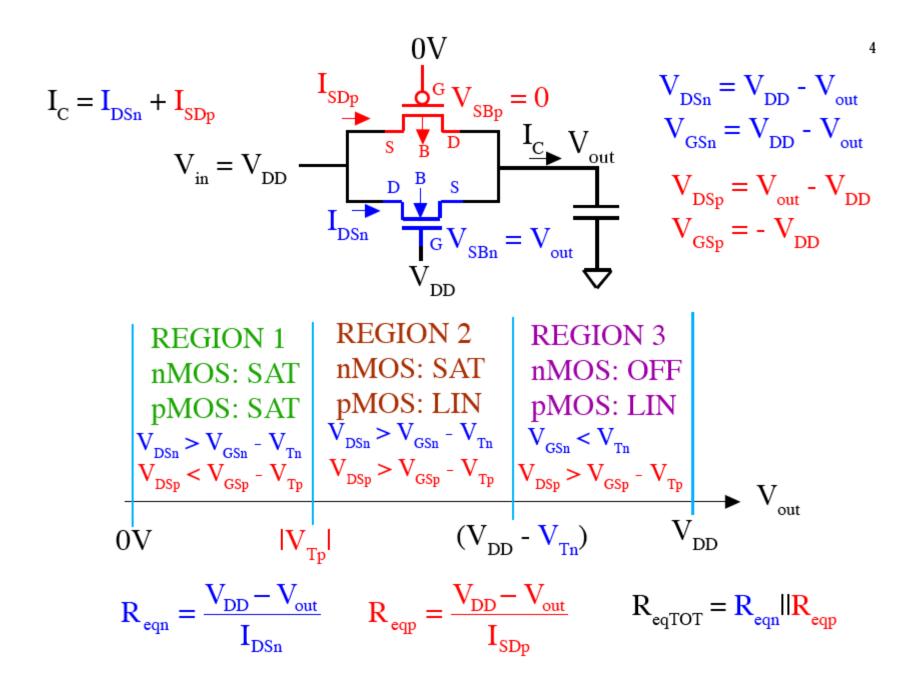

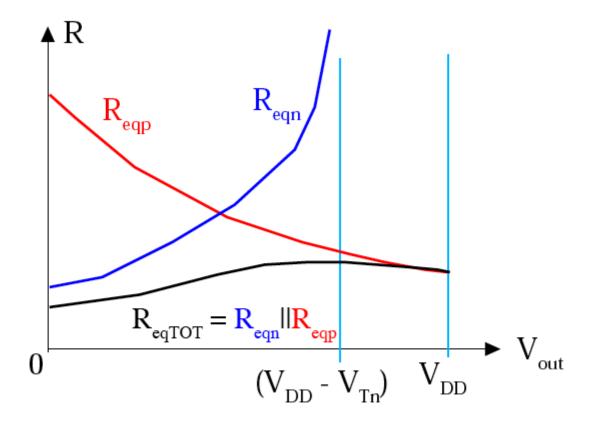

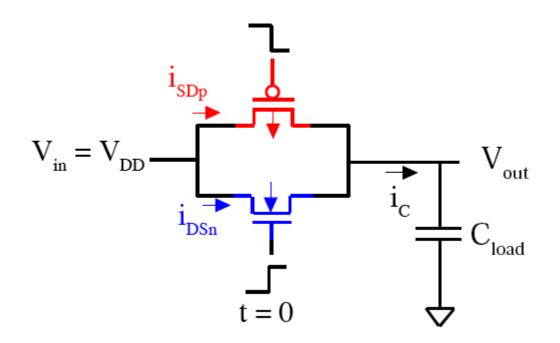

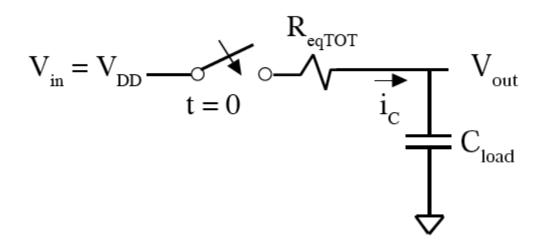

#### SWITCH CHARACTERISTICS

$\frac{\text{Input}}{0} \quad a \longrightarrow b \quad \text{Strong } 0$

1 a \_\_\_\_\_b <u>Strong 1</u>

$$\begin{array}{ll} \begin{array}{ll} \text{REGION 1:} \\ \text{nMOS: SAT} \\ \text{pMOS: SAT} \end{array} & \begin{array}{l} R_{eqn} = \frac{2(V_{DD} - V_{out})}{k_n(V_{DD} - V_{out} - V_{Tn})^2} \\ R_{eqp} = \frac{2(V_{DD} - V_{out})}{k_p(V_{DD} - |V_{Tp}|)^2} \\ \end{array} \\ \begin{array}{l} \text{REGION 2} \\ \text{nMOS: SAT} \end{array} & \begin{array}{l} R_{eqp} = \frac{2(V_{DD} - V_{out})}{k_n(V_{DD} - V_{out} - V_{Tn})^2} \\ R_{eqp} = \frac{2(V_{DD} - V_{out})}{k_p[2(V_{DD} - |V_{Tp}|)(V_{DD} - V_{out}) - (V_{DD} - V_{out})^2]} \\ \end{array} \\ \begin{array}{l} = \frac{2}{k_p[2(V_{DD} - |V_{Tp}|) - (V_{DD} - V_{out})]} \\ \end{array} \\ \begin{array}{l} \text{REGION 3} \\ \text{nMOS: OFF} \\ \text{pMOS: LIN} \end{array} & \begin{array}{l} R_{eqn} = \infty \\ R_{eqp} = \frac{2}{k_p[2(V_{DD} - |V_{Tp}|) - (V_{DD} - V_{out})]} \end{array} \end{array}$$

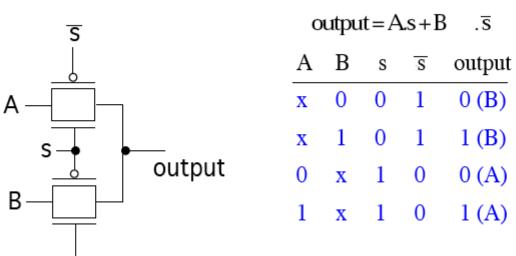

#### **2-INPUT MULTIPLEXER**

S

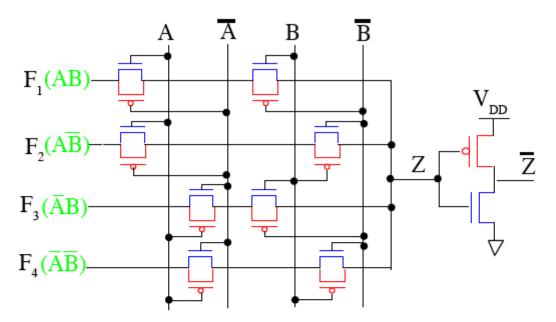

XOR (COMPLEMENTARY PASS-TRANSISTOR LOGIC OR CPL)

SOME OF THE FUNCTIONS REALIZED BY THE BOOLEAN FUNCTION UNIT (CPL)

| OPERATION (Z) | $\mathbf{F}_{1}$ | $F_2$ | F <sub>3</sub> | $F_4$ |

|---------------|------------------|-------|----------------|-------|

| NOR(A,B)      | 0                | 0     | 0              | 1     |

| XOR(A,B)      | 0                | 1     | 1              | 0     |

| NAND(A,B)     | 0                | 1     | 1              | 1     |

| AND(A,B)      | 1                | 0     | 0              | 0     |

| OR(A,B)       | 1                | 1     | 1              | 0     |