## **Digital IC Design and Architecture**

# MOS Inverter Static Characteristics

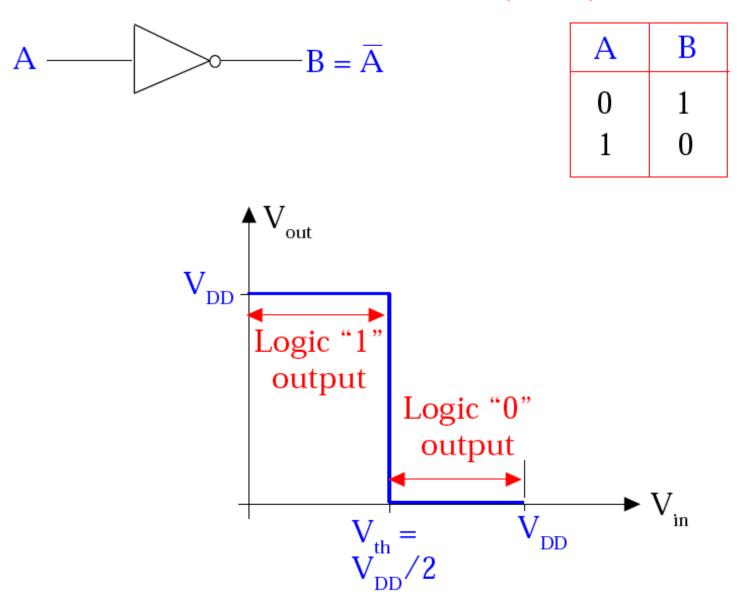

#### IDEAL INVERTER VOLTAGE TRANSFER CHARTERISTIC (VTC)

OH

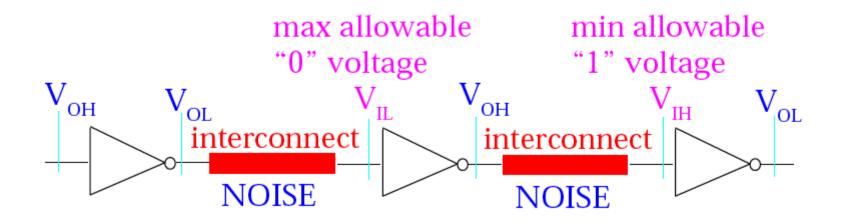

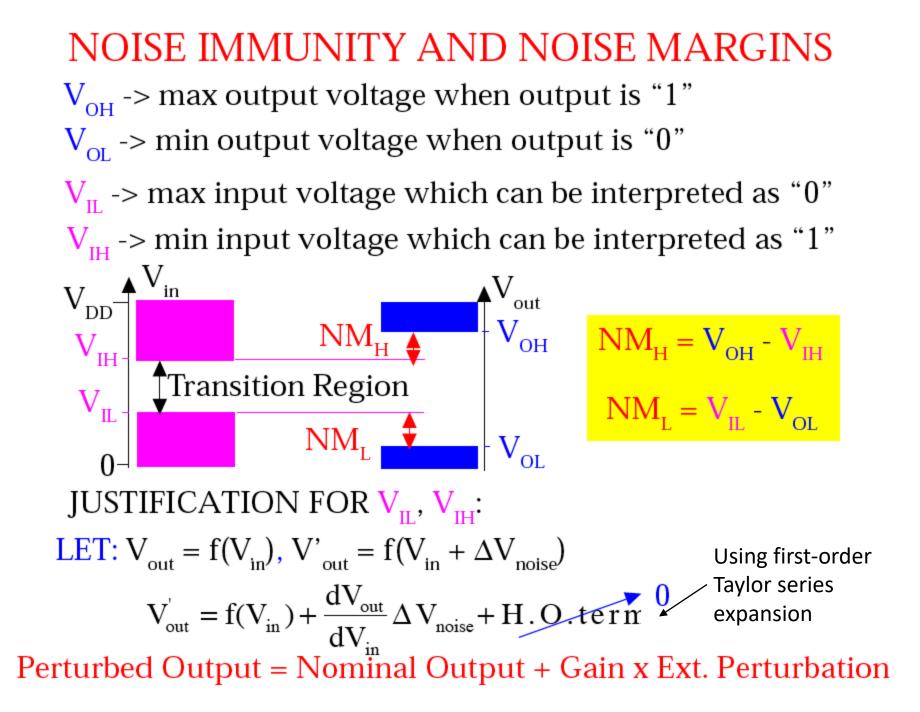

#### NOISE IMMUNITY AND NOISE MARGINS

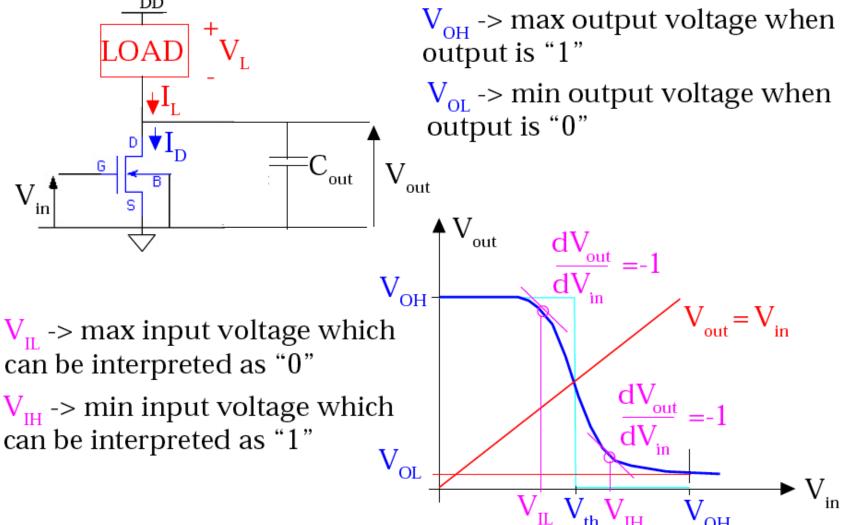

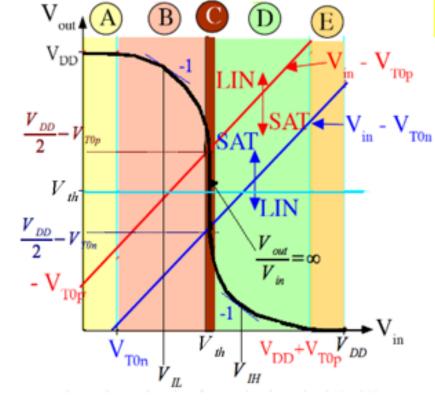

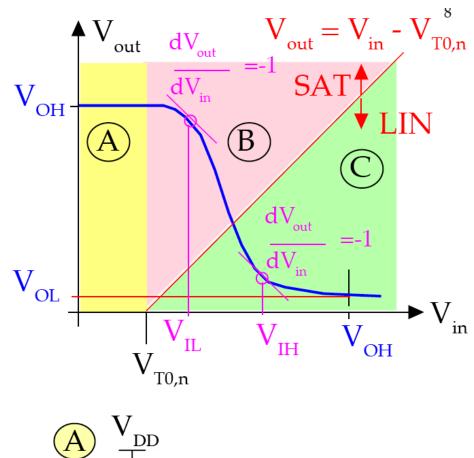

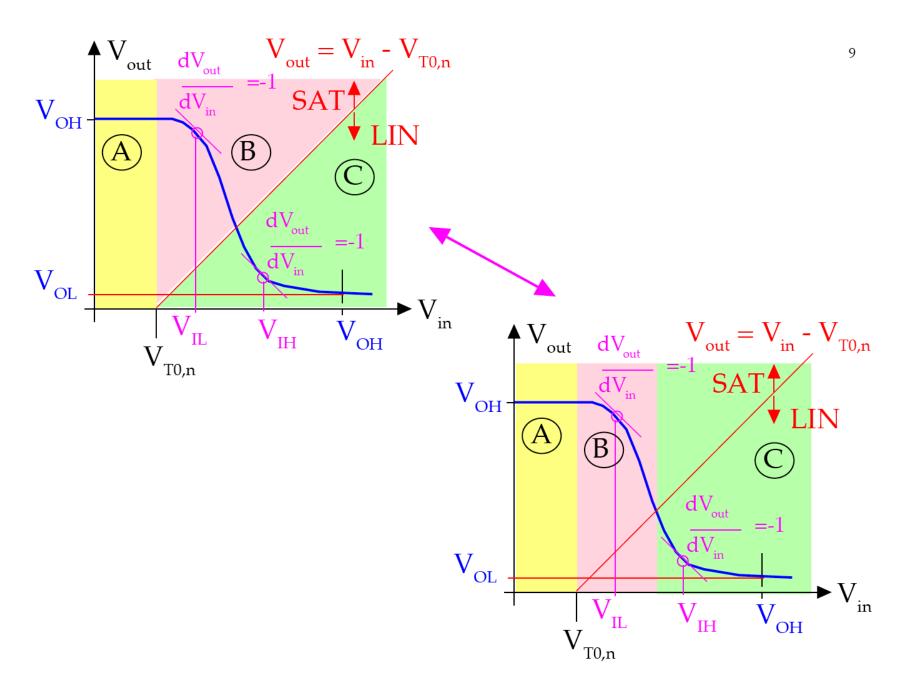

$V_{OH} \rightarrow max$  output voltage when output is "1"  $V_{OL} \rightarrow min$  output voltage when output is "0"  $V_{IL} \rightarrow max$  input voltage which can be interpreted as "0"  $V_{IH} \rightarrow min$  input voltage which can be interpreted as "1"

#### FIVE CRITICAL VOLTAGES: V<sub>OL</sub>, V<sub>OH</sub>, V<sub>IL</sub>, V<sub>IH</sub>, V<sub>th</sub> determine:

- --> DC Output Voltage Behavior

- --> Noise Margins

- --> Width and Location of Transition Region

#### POWER DISSIPATION AND DIE AREA

Power Dissipation -> HEAT

$$T_j = T_a + \Theta P$$

$P \dashrightarrow P_{\rm DC}, P_{\rm dynamic}$

$T_{a} \rightarrow junction Temp$   $T_{a}^{j} \rightarrow ambient Temp$  $\Theta \rightarrow Thermal Resistance$

$$\begin{split} P_{\text{DC}} &= V_{\text{DD}} \ I_{\text{DC}} \\ \textbf{ASSUME:} \ V_{\text{in}} &= ``1`` 50\% \text{ of Op Time, ``0'' 50\% of Op Time} \\ P_{\text{DC}} &= \frac{V_{\text{DD}}}{2} \big[ I_{\text{DC}}(V_{\text{in}} = "0") + I_{\text{DC}}(V_{\text{in}} = "1") \big] \end{split}$$

DIE AREA --> MIN W x L and routing --> limited by design rules

## **Digital IC Design and Architecture**

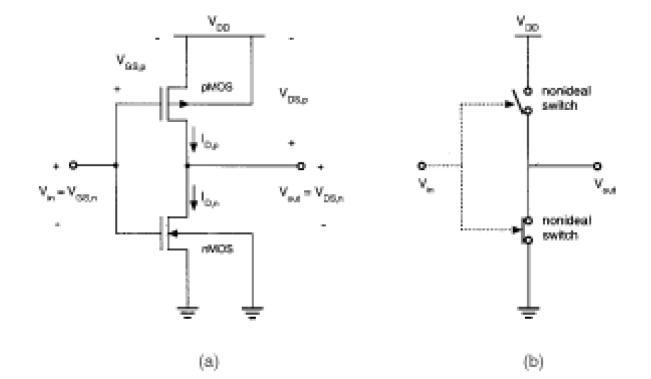

## **CMOS** Inverter

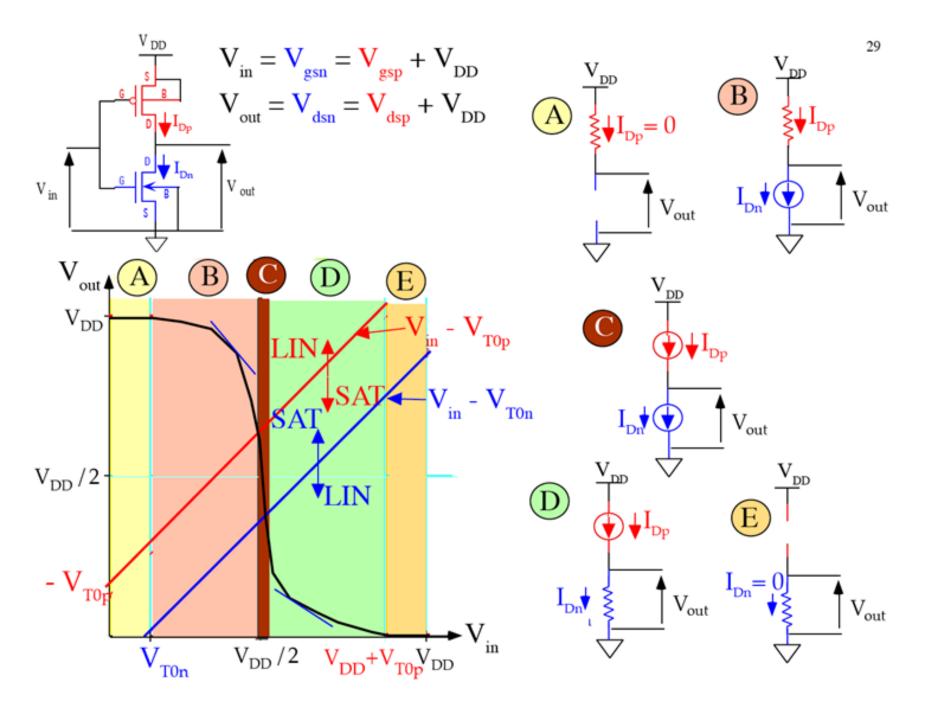

#### **CMOS Inverter Circuit**

### **CMOS Inverter Circuit**

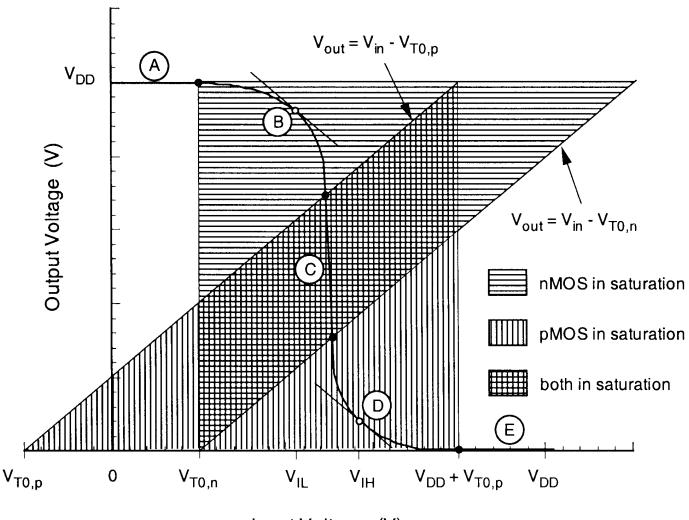

Input Voltage (V)

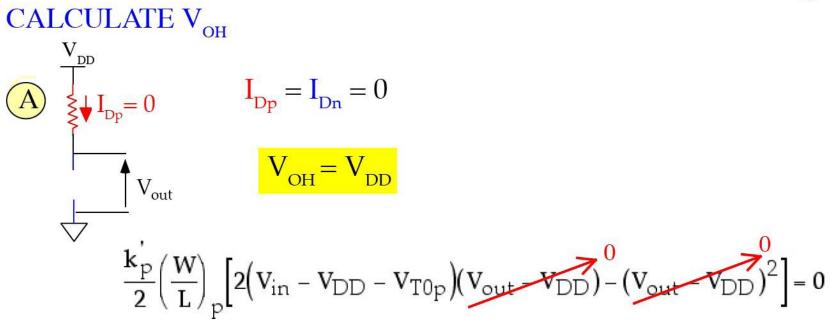

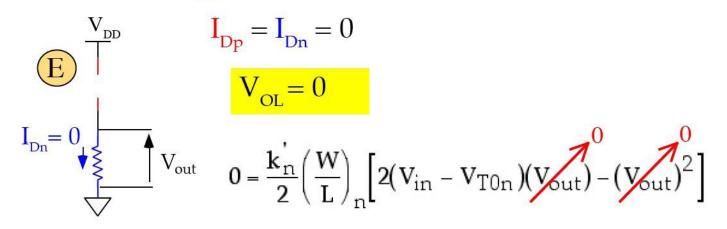

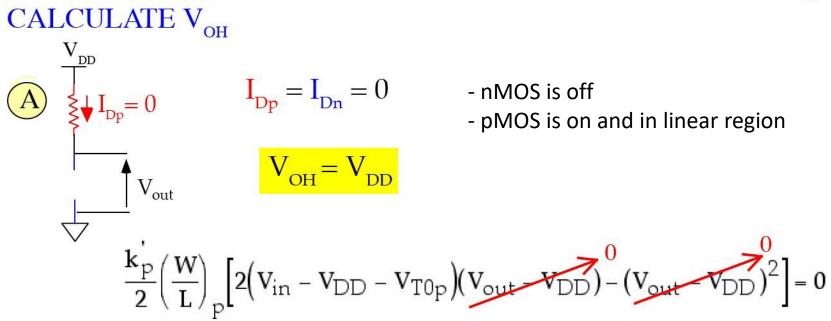

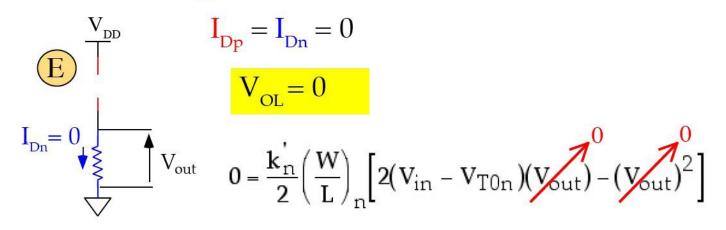

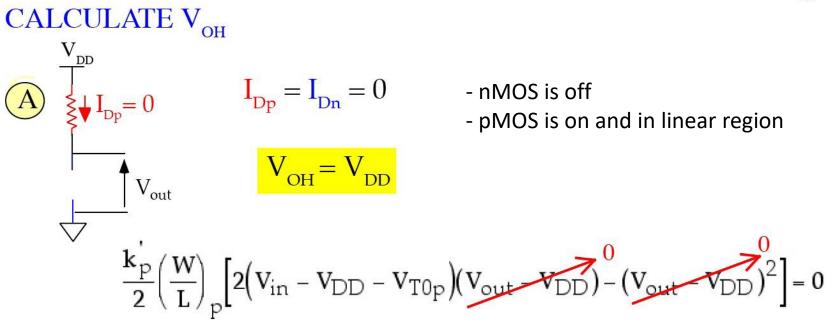

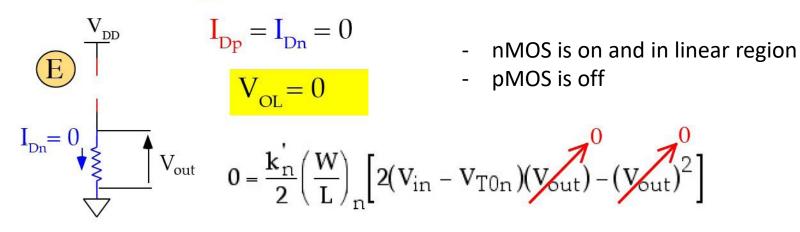

CALCULATE V<sub>OL</sub>

CALCULATE V<sub>OL</sub>

CALCULATE V<sub>OL</sub>

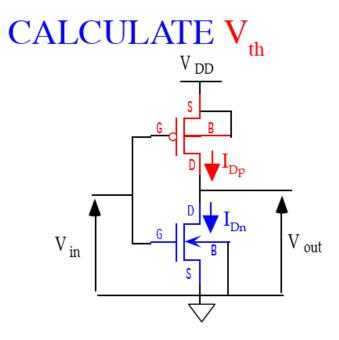

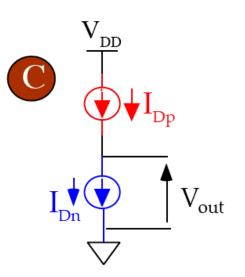

$$\frac{I_{Dp} = I_{Dn}}{2 \left(\frac{W}{L}\right)_{n} \left(V_{GSn} - V_{T0n}\right)^{2}} = \frac{k_{p}}{2} \left(\frac{W}{L}\right)_{p} \left[2\left(V_{GSp} - V_{T0p}\right)V_{DSp} - V_{DSp}^{2}\right]$$

$$V_{GSn} = V_{in'} V_{GSp} = V_{in} - V_{DD'} V_{DSp} = V_{out} - V_{DD}$$

$$\frac{k'_{n}}{2} \left(\frac{W}{L}\right)_{n} (V_{in} - V_{T0n})^{2}$$

$$= \frac{k'_{p}}{2} \left(\frac{W}{L}\right)_{p} \left[2(V_{in} - V_{DD} - V_{T0p})(V_{out} - V_{DD}) - (V_{out} - V_{DD})^{2}\right]$$

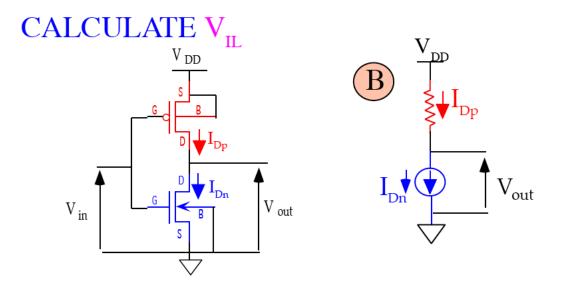

nMOS is in saturation region pMOS is in linear region

$$\frac{\mathbf{I}_{Dp} = \mathbf{I}_{Dn}}{2\left(\frac{W}{L}\right)_{n} \left(V_{GSn} - V_{T0n}\right)^{2}} = \frac{k'_{p}}{2} \left(\frac{W}{L}\right)_{p} \left[2\left(V_{GSp} - V_{T0p}\right)V_{DSp} - V_{DSp}^{2}\right]$$

$$V_{GSn} = V_{in'} V_{GSp} = V_{in} - V_{DD'} V_{DSp} = V_{out} - V_{DD}$$

$$\frac{k'_{n}}{2} \left(\frac{W}{L}\right)_{n} (V_{in} - V_{T0n})^{2}$$

$$= \frac{k'_{p}}{2} \left(\frac{W}{L}\right)_{p} \left[2(V_{in} - V_{DD} - V_{T0p})(V_{out} - V_{DD}) - (V_{out} - V_{DD})^{2}\right]$$

$$\frac{k_{n}}{2} \left(\frac{W}{L}\right)_{n} \left(V_{in} - V_{T0 n}\right)^{2}$$

$$= \frac{k_{p}}{2} \left(\frac{W}{L}\right)_{p} \left[2\left(V_{in} - V_{DD} - V_{T0 p}\right)\left(V_{out} - V_{DD}\right) - \left(V_{out} - V_{DD}\right)^{2}\right]$$

(5.59)

$$DIFFERENTIATING wrt V_{in}$$

$$k_{n}^{'} \left(\frac{W}{L}\right)_{n} \left(V_{in}^{'} - V_{T0 n}\right) = k_{p}^{'} \left(\frac{W}{L}\right)_{p} \left[\left(V_{out} - V_{DD}\right) + \left(V_{in}^{'} - V_{DD} - V_{T0 p}\right)\frac{dV_{out}^{'}}{dV_{in}}\right]$$

$$-\left(V_{out} - V_{DD}\right)\frac{dV_{out}}{dV_{in}} \int_{-1}^{-1}$$

$$k_{n}^{'} \left(\frac{W}{L}\right)_{n} \left(V_{IL} - V_{T0 n}\right) = k_{p}^{'} \left(\frac{W}{L}\right)_{p} \left[2V_{out} - V_{IL} + V_{T0 p} - V_{DD}\right]$$

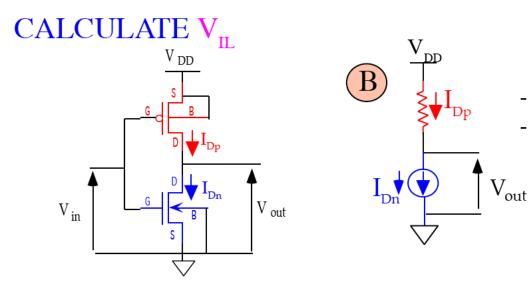

SOLVING FOR V<sub>IL</sub>

$$V_{IL} = \frac{2(V_{out} + V_{T0p} - V_{DD} + k_R V_{T0n}}{1 + k_R} \quad \text{where} \quad k_R = \frac{k_n^{'}(W/L)_n}{k_p^{'}(W/L)_p} \quad (5.62)$$

SOLVE Eqs (5.59) and (5.62) for  $V_{out}$  and  $V_{IL}$

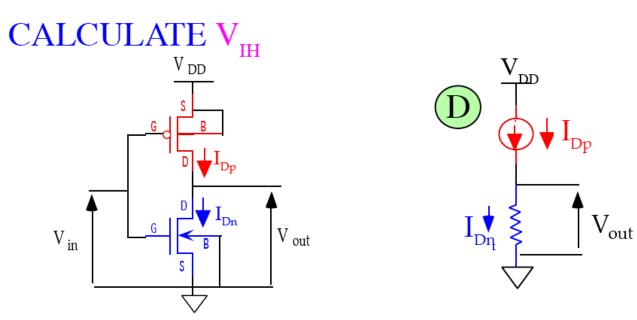

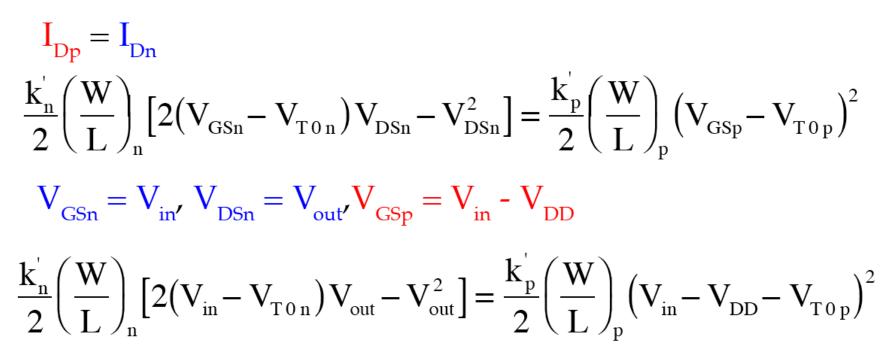

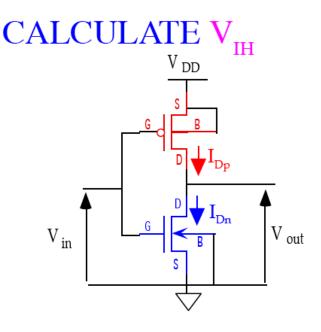

- nMOS is in linear region

- pMOS is in saturation region

$$\frac{\kappa_{n}}{2} \left(\frac{w}{L}\right)_{n} \left[2\left(V_{in} - V_{T0n}\right)V_{out} - V_{out}^{2}\right] = \frac{\kappa_{p}}{2} \left(\frac{w}{L}\right)_{p} \left(V_{in} - V_{DD} - V_{T0p}\right)^{2}$$

$$\frac{k'_{n}}{2} \left(\frac{W}{L}\right)_{n} \left[2(V_{in} - V_{T0n})V_{out} - V_{out}^{2}\right] = \frac{k'_{p}}{2} \left(\frac{W}{L}\right)_{p} \left(V_{in} - V_{DD} - V_{T0p}\right)^{2} (5.64)$$

DIFFERENTIATING wrt V<sub>in</sub>

$$k'_{n} \left(\frac{W}{L}\right)_{n} \left[ \left(V'_{in} - V_{TO n}\right) \frac{dV'_{out}}{dV_{in}} + V_{out} - V_{out} \frac{dV'_{out}}{dV_{in}} \right] = k'_{p} \left(\frac{W}{L}\right)_{p} \left(V'_{in} - V_{DD} - V_{TO p}\right)$$

$$\mathbf{k}_{n}^{'}\left(\frac{W}{L}\right)_{n}\left[-V_{IH}+V_{T0n}+2V_{out}\right] = \mathbf{k}_{p}^{'}\left(\frac{W}{L}\right)_{p}\left(V_{IH}-V_{DD}-V_{T0p}\right)$$

SOLVING FOR  $\mathrm{V}_{\mathrm{IH}}$

$$V_{IH} = \frac{V_{DD} + V_{T0p} + k_R (2V_{out} + V_{T0n})}{1 + k_R}$$

(5.67)

where  $k_R = \frac{k'_n (W/L)_n}{k'_p (W/L)_p}$

SOLVE Eqs. (5.64) and (5.67) for  $V_{_{\rm out}}$  and  $V_{_{\rm IH}}$

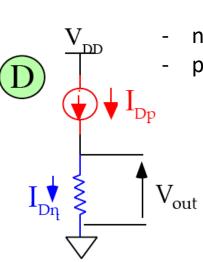

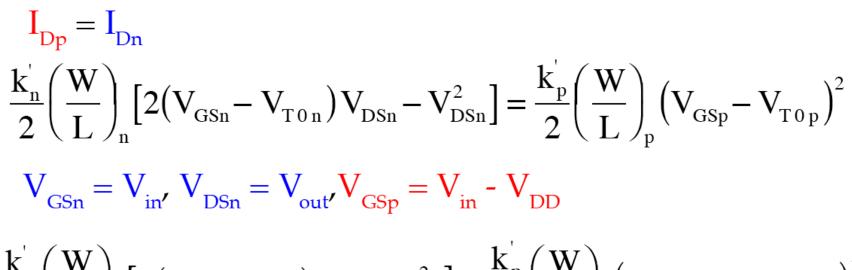

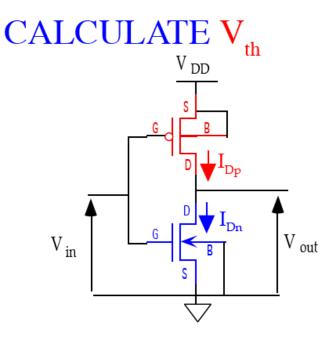

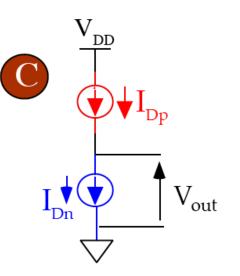

$$\frac{\mathbf{I}_{Dp} = \mathbf{I}_{Dn}}{2} \left(\frac{W}{L}\right)_{n} \left(V_{GSn} - V_{T0n}\right)^{2} = \frac{k_{p}}{2} \left(\frac{W}{L}\right)_{p} \left(V_{GSp} - V_{T0p}\right)^{2}$$

$$V_{GSn} = V_{in'} V_{GSp} = V_{in} - V_{DD}$$

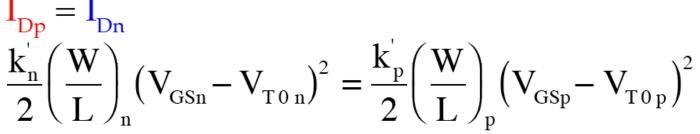

$$\frac{k'_{n}}{2} \left(\frac{W}{L}\right)_{n} \left(V_{in} - V_{T0n}\right)^{2} = \frac{k'_{p}}{2} \left(\frac{W}{L}\right)_{p} \left(V_{in} - V_{DD} - V_{T0p}\right)^{2}$$

- nMOS is in saturation region

- pMOS is in saturation region

$$\frac{V_{GSn} = V_{in'} V_{GSp} = V_{in} - V_{DD}}{\frac{k'_{n}}{2} \left(\frac{W}{L}\right)_{n} \left(V_{in} - V_{T0n}\right)^{2}} = \frac{k'_{p}}{2} \left(\frac{W}{L}\right)_{p} \left(V_{in} - V_{DD} - V_{T0p}\right)^{2}$$

$$\frac{\dot{k_{n}}}{2} \left(\frac{W}{L}\right)_{n} (V_{in} - V_{T0n})^{2} = \frac{\dot{k_{p}}}{2} \left(\frac{W}{L}\right)_{p} (V_{in} - V_{DD} - V_{T0p})^{2}$$

SOLVING for  $V_{th} = V_{in}$

$$V_{in} = V_{th} = \frac{V_{T0n} + \sqrt{\frac{1}{k_{R}}}(V_{DD} + V_{T0p})}{\left(1 + \sqrt{\frac{1}{k_{R}}}\right)}$$

RECALL THAT  $V_{th} = V_{in} = V_{out}$

$\sqrt{k_R}$

37

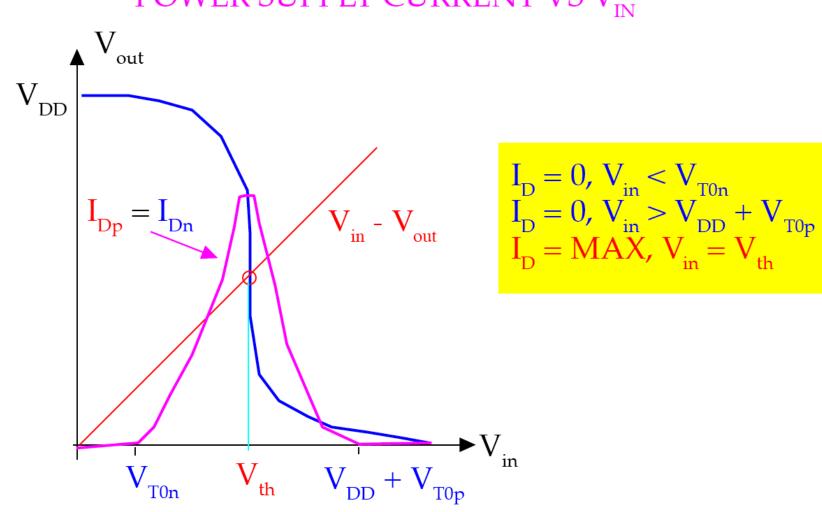

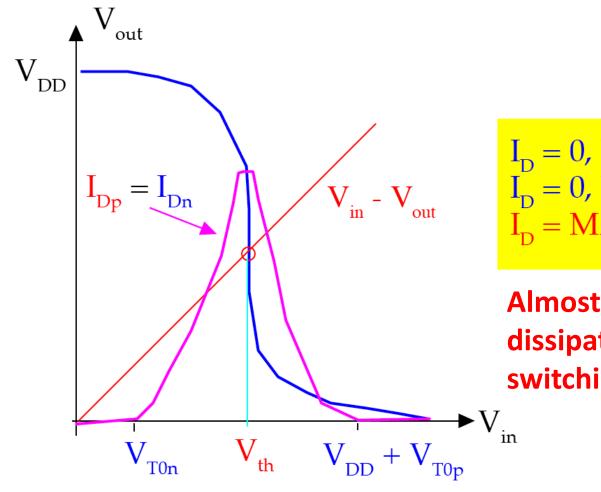

#### POWER SUPPLY CURRENT VS $V_{IN}$

$$I_{D} = 0, V_{in} < V_{T0n} I_{D} = 0, V_{in} > V_{DD} + V_{T0p} I_{D} = MAX, V_{in} = V_{th}$$

Almost all power is dissipated during the switching!

DESIGN OF CMOS INVERTERS

$$V_{in} = V_{th} = \frac{V_{T0n} + \sqrt{\frac{1}{k_R}} (V_{DD} + V_{T0p})}{\left(1 + \sqrt{\frac{1}{k_R}}\right)}$$

SOLVING FOR  $k_R$

$k_R = \left(\frac{V_{DD} + V_{T0p} - V_{th}}{V_{th} - V_{T0n}}\right)^2$

FOR IDEAL INVERTER  $V_{th} = \frac{1}{2}V_{DD}$

$\left(1 - \frac{1}{2}\right) = \left(\frac{0.5 V_{DD} + V_{T0p}}{V_{T0p}}\right)^2$

$$(k_{R})_{ideal} = \begin{pmatrix} 0.5 V_{DD} + V_{T0p} \\ 0.5 V_{DD} - V_{T0n} \end{pmatrix}$$

IF  $V_{T0} = V_{T0n} = -V_{T0p} \implies (k_{R})_{inverter}^{symmetric} =$

$$k_{R} = \frac{k_{n}^{'}(W/L)_{n}}{k_{p}^{'}(W/L)_{p}} = \frac{\mu_{n}C_{ox}(W/L)_{n}}{\mu_{p}C_{ox}(W/L)_{p}} = \frac{\mu_{n}(W/L)_{n}}{\mu_{p}(W/L)_{p}}$$

FOR SYMMETRIC INVERTER  $V_{T0} = V_{T0n} = -V_{T0p}$   $(k_R)_{inverter}^{symmetric} = 1$

$$\begin{aligned} \frac{(W/L)_{n}}{(W/L)_{p}} = k_{R} \frac{\mu_{p}}{\mu_{n}} \xrightarrow{k_{R}=1} \underbrace{(W/L)_{n}}_{(W/L)_{p}} = \frac{\mu_{p}}{\mu_{n}} \\ \frac{(W/L)_{n}}{(W/L)_{p}} = \frac{\mu_{p}}{\mu_{n}} = \frac{230 \text{ cm}^{2}/\text{Vs}}{580 \text{ cm}^{2}/\text{Vs}} \xrightarrow{(W/L)_{p}} \underbrace{(W/L)_{p}}_{(W/L)_{p}} = 2.5(W/L)_{n} \\ V_{IL} = \frac{1}{8} (3 \text{ V}_{DD} + 2 \text{ V}_{T0}) \\ V_{IL} = \frac{1}{8} (5 \text{ V}_{DD} - 2 \text{ V}_{T0}) \\ V_{IH} = \frac{1}{8} (5 \text{ V}_{DD} - 2 \text{ V}_{T0}) \\ NOTE: \text{ V}_{IL} + \text{ V}_{IH} = \text{ V}_{DD} \\ NM_{H} = \text{ V}_{OH} - \text{ V}_{IH} = \text{ V}_{DD} - \text{ V}_{IH} = (3/8) \text{ V}_{DD} + (2/8) \text{ V}_{T0} \\ NM_{L} = \text{ V}_{IL} - \text{ V}_{OL} = \text{ V}_{IL} = (3/8) \text{ V}_{DD} + (2/8) \text{ V}_{T0} \end{aligned}$$

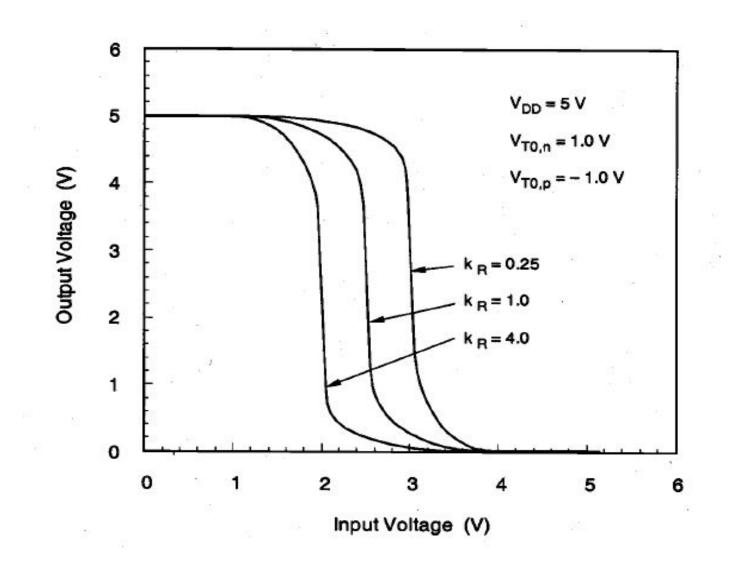

#### VTC for three CMOS inverters with different nMOS-pMOS ratios

POWER DISSIPATION CONSIDERATIONS

$$P_{DC} = \frac{V_{DD}}{2} \left[ I_{DC}(V_{in} = "0") + I_{DC}(V_{in} = "1") \right] = \frac{P(V_{in} = 0) + P(V_{in} = 1)}{2}$$

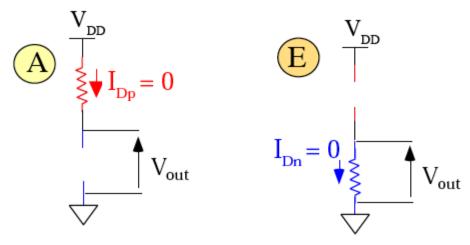

WHEN  $V_{in} = V_{OL}$ :  $I_{L} = I_{D} = 0 \implies P(V_{in} = 0) = 0$

WHEN  $V_{in} = V_{OH}$ :  $I_{L} = I_{D} = 0 \implies P(V_{in} = 1) = 0$

$$P_{DC} = 0$$

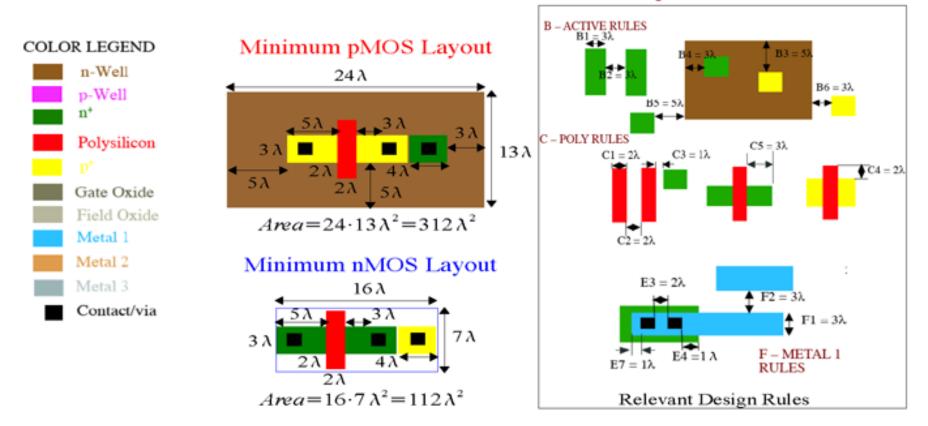

#### Minimum Area MOS Transistor Layouts

7

#### DIE AREA CONSIDERATIONS $\mathbf{V}_{\mathrm{in}}$ COLOR LEGEND n-Well $n^+$ Polysilicon Metal 1 $\mathbf{V}_{\mathrm{DD}}$ GND V Contact/via out $\mathbf{V}_{\mathrm{in}}$ GND $V_{DD}$ V out

## **Digital IC Design and Architecture**

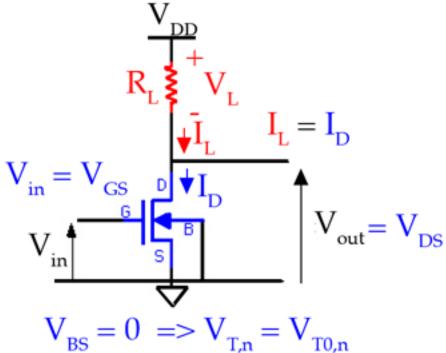

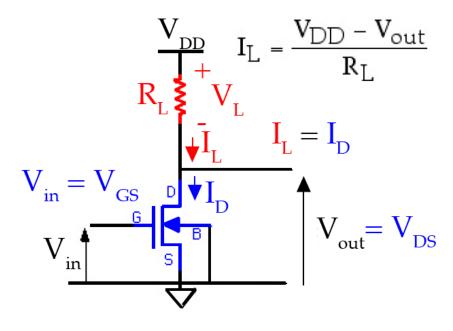

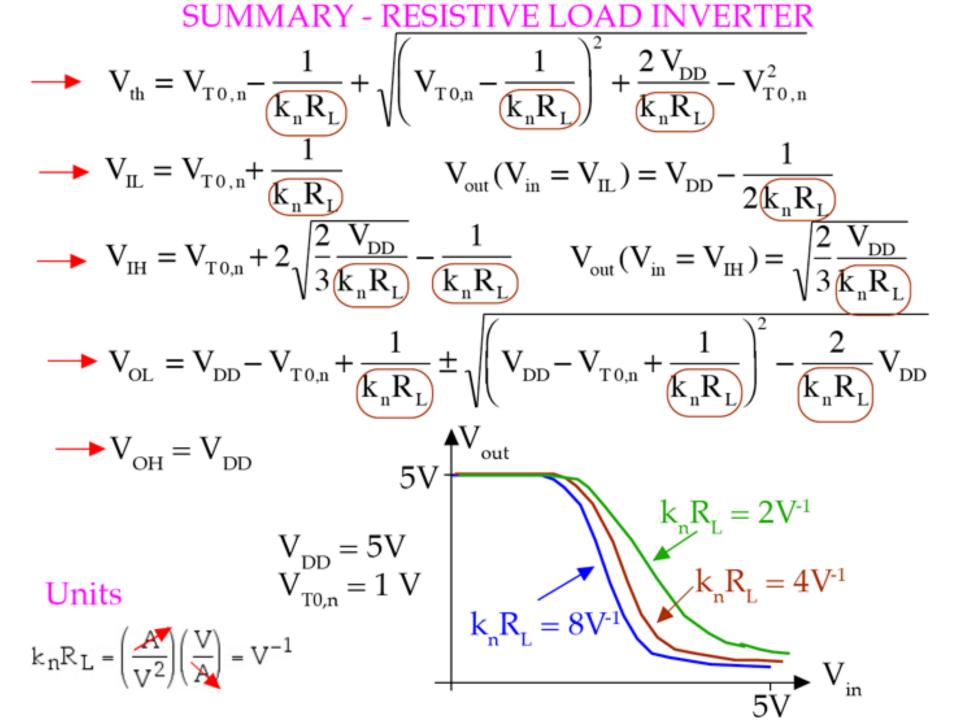

## Resistive Load Inverter

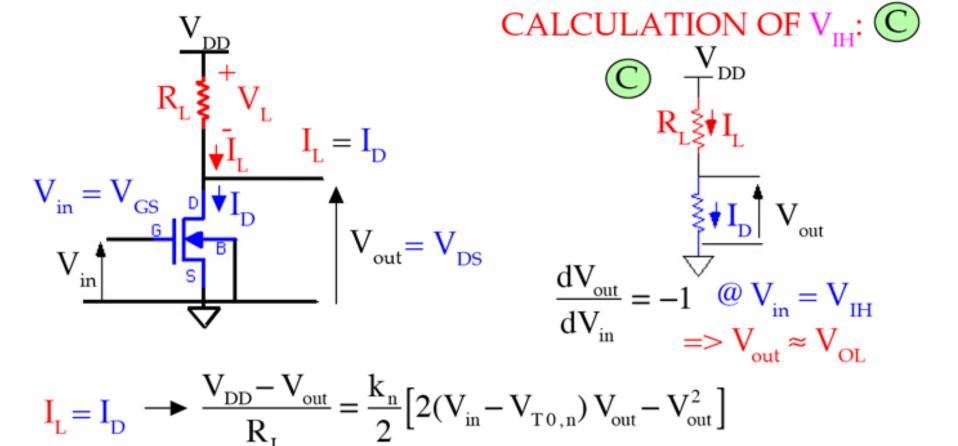

**RESISTIVE-LOAD INVERTER**

CUTOFF:

$$V_{in} = V_{GS} < V_{T0,n'} I_D = 0$$

LINEAR:  $V_{in} = V_{GS} \ge V_{T0,n'} V_{un} = V_{DS} \le V_{in} - V_{t0,n}$

$$I_{\rm D} = \frac{k_{\rm n}}{2} \Big[ 2(V_{\rm in} - V_{\rm T0,n}) V_{\rm out} - V_{\rm out}^2 \Big]$$

SATURATION:

$$V_{in} = V_{GS} \ge V_{T0,n}$$

$$V_{out} = V_{DS} > V_{in} - V_{T0,n}$$

$$I_{D} = \frac{k_{n}}{2} (V_{in} - V_{T0,n})^{2}$$

Units

$$k_{n} = \left(\frac{\mathrm{cm}^{2}}{\mathrm{V}\,\mathrm{sec}}\right) \left(\frac{\mathrm{F}}{\mathrm{cm}^{2}}\right) = \left(\frac{\mathrm{cm}^{2}}{\mathrm{V}\,\mathrm{sec}}\right) \left(\frac{\mathrm{C}}{\mathrm{V}\,\mathrm{cm}^{2}}\right)$$

$$= \left(\frac{\mathrm{C}/\,\mathrm{sec}}{\mathrm{V}^{2}}\right) = \frac{\mathrm{A}}{\mathrm{V}^{2}}$$

Let (for hand calculations)  $\lambda = 0$

Where:  $k_n = \mu_n C_{ox} \frac{W}{L}$ RESISTOR R.:

$$I_{L} = \frac{V_{DD} - V_{out}}{R_{L}}$$

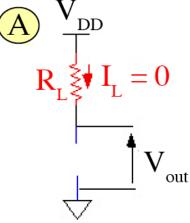

CALCULATION OF  $V_{OH}$ :  $V_{out} = V_{DD} - R_L I_L$   $V_{in} < V_{T0,n} => nMOS Cut-off$  $I_D = I_L = 0 => V_{OH} = V_{DD}$

$$V_{in} = V_{CS} \bigvee_{I_{L}} = I_{D} \\ V_{in} = V_{CS} \bigvee_{I_{L}} = V_{DS} \\ V_{in} = V_{CS} \bigvee_{I_{L}} = V_{DS} \\ V_{in} = V_{CS} \bigvee_{I_{D}} \bigvee_{I_{D}} \bigvee_{I_{D}} = V_{DS} \\ V_{in} = V_{CS} \bigvee_{I_{D}} \bigvee$$

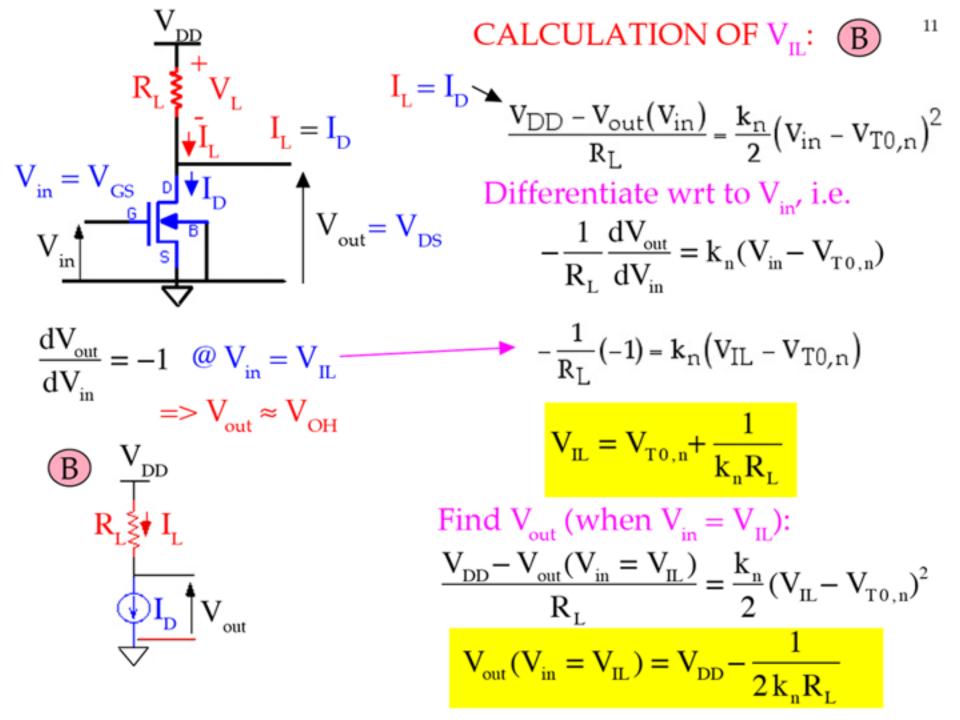

Differentiate wrt to

$$V_{in'}$$

i.e.

$$-\frac{1}{R_L} \frac{dV_{out}}{dV_{in}}^{-1} = \frac{k_n}{2} \left[ 2(V_{in} - V_{TO,n}) \frac{dV_{out}}{dV_{in}} + 2V_{out} - 2V_{out} \frac{dV_{out}}{dV_{in}} \right]$$

$$V_{IH} = V_{TO,n} + 2V_{out} - \frac{1}{k_n R_L}$$

CALCULATION OF

$$V_{H}$$

:

$$V_{DD}$$

$$R_{L} \neq I_{L}$$

$$V_{DD} - V_{out}$$

$$V_{DD} - V_{out} = \frac{k_{n}}{2} \left[ 2(V_{H} - V_{T0,n}) V_{out} - V_{out}^{2} \right]$$

$$Where$$

$$V_{H} = V_{T0,n} + 2 V_{out} - \frac{1}{k_{n}R_{L}}$$

$$\frac{V_{DD} - V_{out}}{R_{L}} = \frac{k_{n}}{2} \left[ 2(V_{T0,n} + 2 V_{out} - \frac{1}{k_{n}R_{L}} - V_{T0,n}) V_{out} - V_{out}^{2} \right]$$

$$\frac{V_{DD} - V_{out}}{R_{L}} = \frac{k_{n}}{2} \left[ 3V_{out}^{2} - \frac{2V_{out}}{k_{n}R_{L}} \right]$$

$$\frac{V_{DD} - V_{out}}{R_{L}} = \frac{3}{2} k_{n} V_{out}^{2} \longrightarrow V_{out} (V_{in} = V_{H}) = \sqrt{\frac{2}{3} \frac{V_{DD}}{k_{n}R_{L}}}$$

CALCULATION OF

$$V_{th}$$

:

$V_{in} = V_{out} = V_{th} => V_{DS} = V_{GS} > V_{GS} - V_{T0,n} \longrightarrow \mathbb{B}$

$I_{L} = I_{D} \longrightarrow \frac{V_{DD} - V_{out}}{R_{L}} = \frac{k_{n}}{2} (V_{m}^{V_{th}} - V_{T0,n})^{2}$

$\frac{V_{DD} - V_{th}}{R_{L}} = \frac{k_{n}}{2} (V_{th} - V_{T0,n})^{2}$

$V_{th}^{2} - 2 \left( V_{T0,n} - \frac{1}{k_{n}R_{L}} \right) V_{th} + V_{T0,n}^{2} - \frac{2V_{DD}}{k_{n}R_{L}} = 0$

$V_{th} = V_{T0,n} - \frac{1}{k_{n}R_{L}} \pm \sqrt{\left( V_{T0,n} - \frac{1}{k_{n}R_{L}} \right)^{2} + \frac{2V_{DD}}{k_{n}R_{L}} - V_{T0,n}^{2}}$

POWER DISSIPATION - RESISTIVE LOAD INVERTER <sup>16</sup>

$$P_{DC} = \frac{V_{DD}}{2} \left[ I_{DC} (V_{in} = "0") + I_{DC} (V_{in} = "1") \right]$$

WHEN  $V_{in} = V_{OL}$ : DRIVER nMOS in CUT-OFF  $I_L = I_D = 0 \implies P(V_{in} = 0) = 0$

WHEN

$$V_{in} = V_{OH}$$

:

$I_{DC}(V_{in} = "1") = I_L = I_D = \frac{V_{DD} - V_{OL}}{R_L}$

$P(V_{in} = "1") = \frac{V_{DD}}{2} \frac{V_{DD} - V_{OL}}{R_L}$

$$P_{DC}(average) = \frac{V_{DD}}{2} \frac{V_{DD} - V_{OL}}{R_{L}}$$

$$\mathbf{A} \mathbf{V}_{DD}$$

$$\mathbf{R}_{L} \mathbf{V}_{DL} = \mathbf{0}$$

$$\mathbf{V}_{out}$$

$$\mathbf{V}_{DD}$$

$$\mathbf{V}_{DD}$$

$$\mathbf{R}_{L} \mathbf{V}_{IL}$$

$$\mathbf{V}_{out}$$

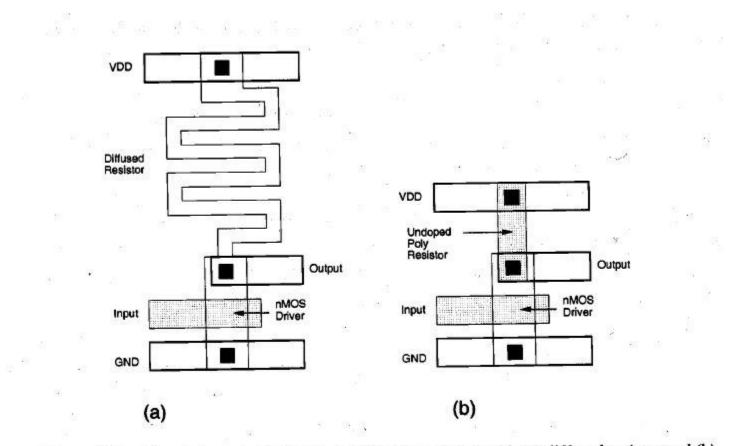

# Two examples of resistive load inverter layout are shown below:

Figure 5.10. Sample layout of resistive-load inverter circuits with (a) diffused resistor and (b) undoped polysilicon resistor.

## **Digital IC Design and Architecture**

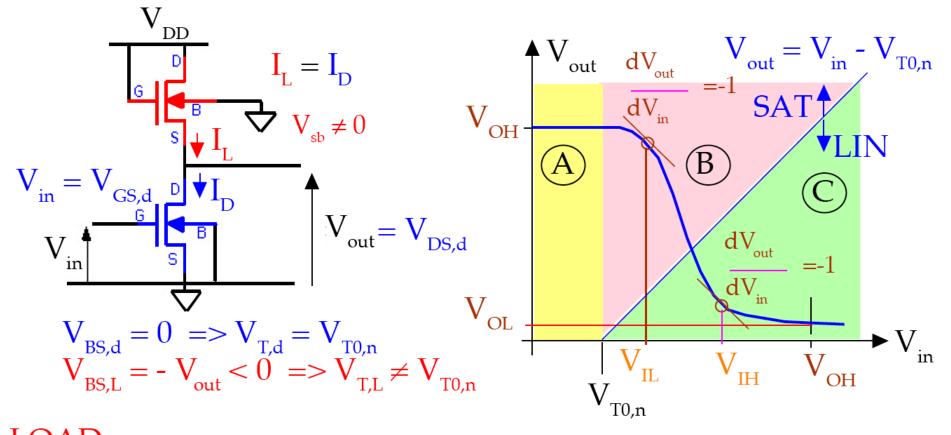

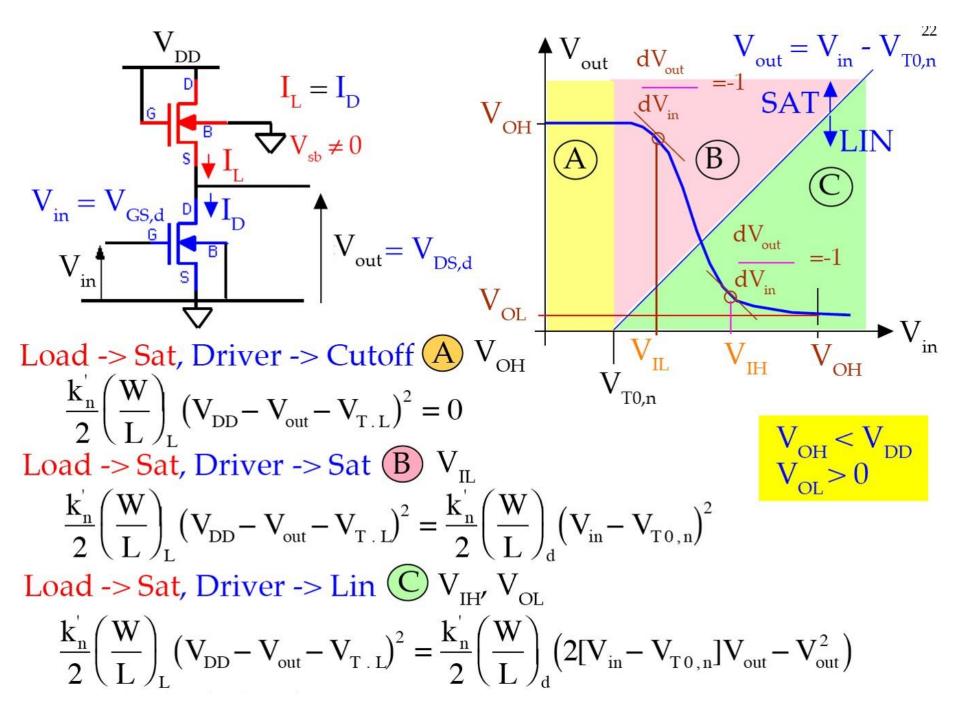

# Saturated Enhancement Load Inverter

SATURATED ENHANCEMENT-LOAD INVERTER

LOAD:  $V_{GS,L} = V_{DS,L} => V_{DS,L} > V_{GS,L} - V_{T,L}$  SAT cond. is ALWAYS SATISFIED

$$I_{L} = \frac{k'_{n}}{2} \left(\frac{W}{L}\right)_{L} \left(V_{GS,L} - V_{T.L}\right)^{2} = \frac{k'_{n}}{2} \left(\frac{W}{L}\right)_{L} \left(V_{DD} - V_{out} - V_{T.L}\right)^{2}$$

- Saturated Enhancement Load Inverters require relatively high stand-by DC power dissipation

- Because of this high stand-by DC power dissipation the Enhancement-load nMOS inverters are not used in any large-scale digital applications

Textbook examples to be reviewed:

Examples 5.1 and 5.2 – Resistive Load Inverter

Example 5.4 – nMOS with pMOS Load Inverter