# Digital Integrated Circuit Design and Architecture

Chapter 2: Fabrication of MOSFETs

## **CMOS ICs Fabrication**

- CMOS transistors and CMOS ICs are fabricated on silicon wafers

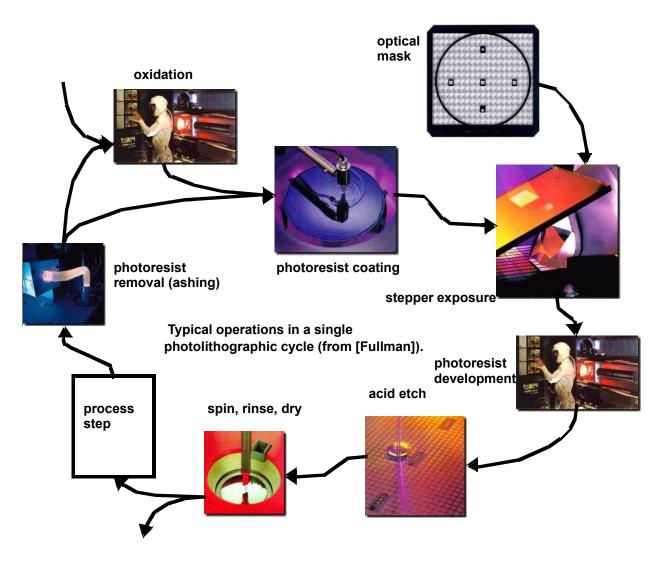

- Photo-Lithography process is used for the fabrication and it is similar to printing press

- On each step of different materials are deposited or etched

## Silicon Ingot

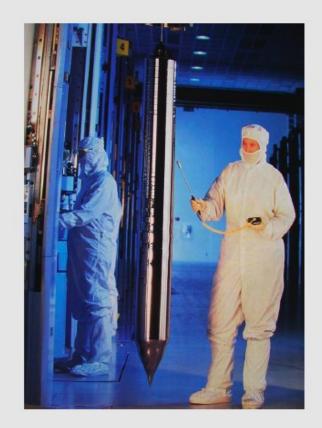

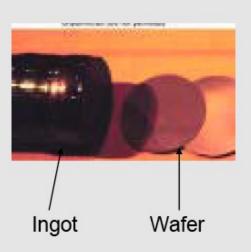

#### **Silicon Ingot and Wafer Manufacturing**

From Smithsonian, 2000

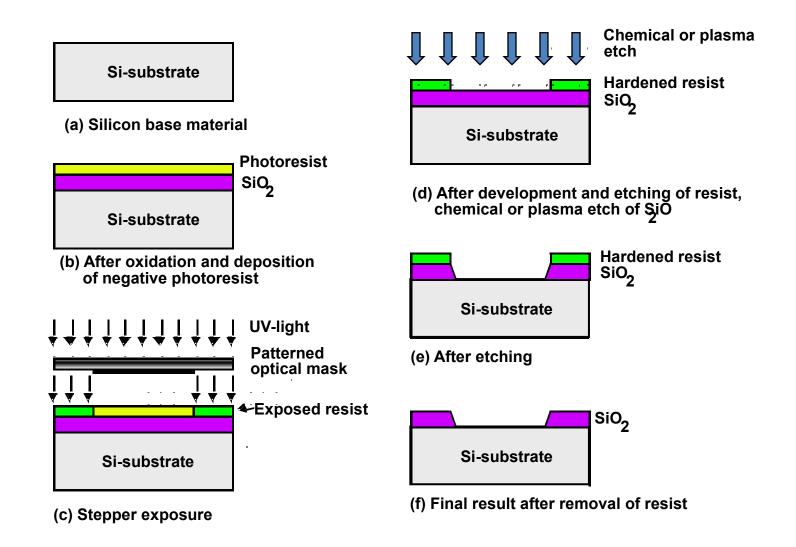

## **Photo-Lithographic Process**

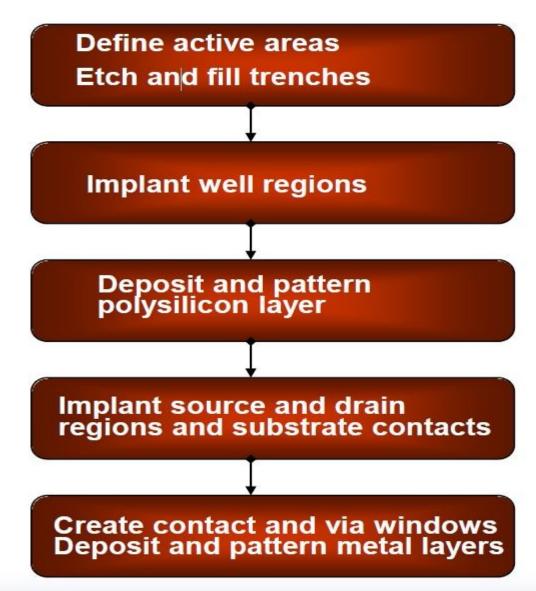

## **CMOS** Process insight

## Patterning of SiO2 – Basic Steps

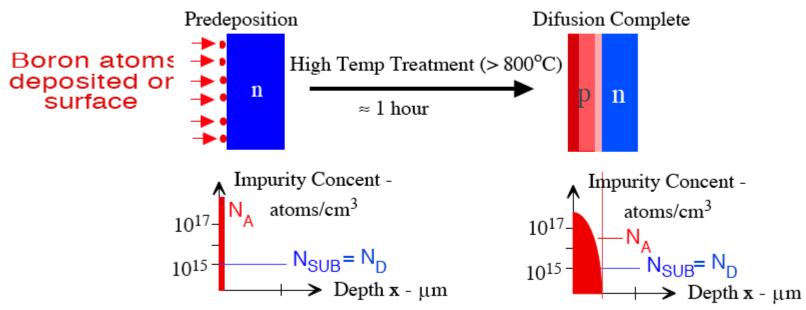

## **Creating Diffusion Regions**

#### CMOS PROCESSING TECHNOLOGY

DIFFUSION PROCESS

-> Boron typically used for p-type doping

-> Arsenic and Phosphorus are typically used for n-type doping.

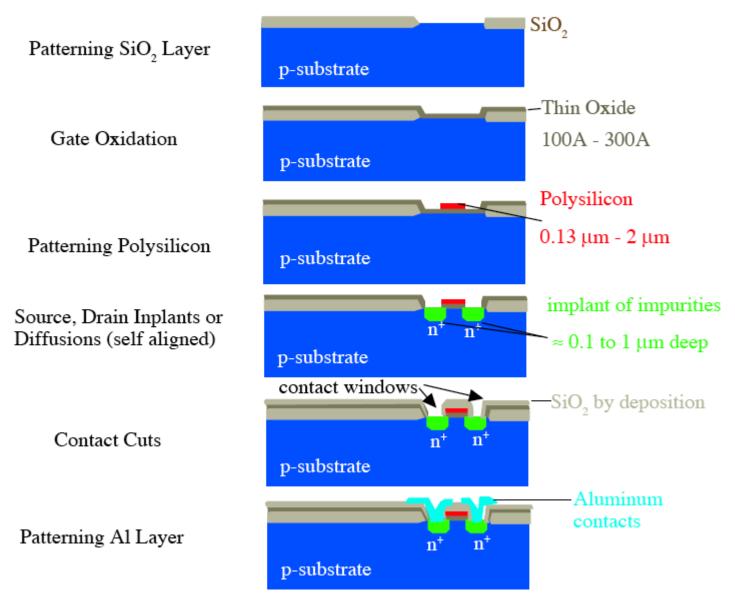

#### Fabrication Steps in Si-Gate (self-aligned) NMOS Process

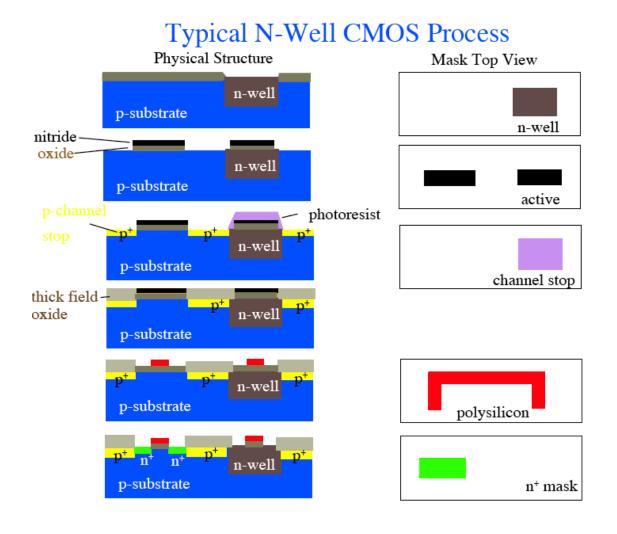

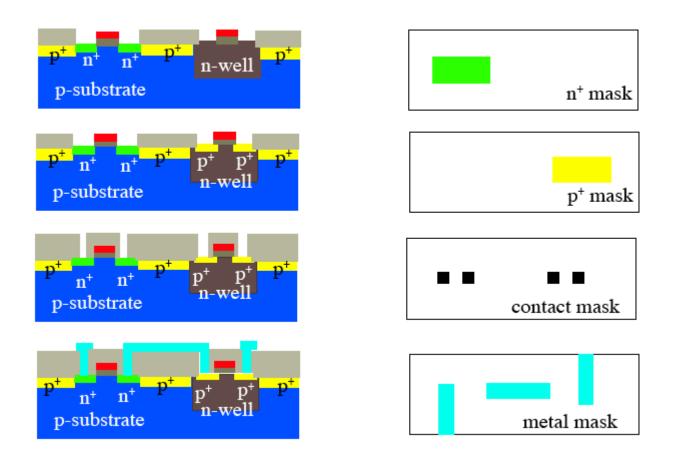

## **CMOS Process Walk-Through**

#### Fabrication of nMOS and pMOS transistors process example

## **CMOS Process Walk-Through**

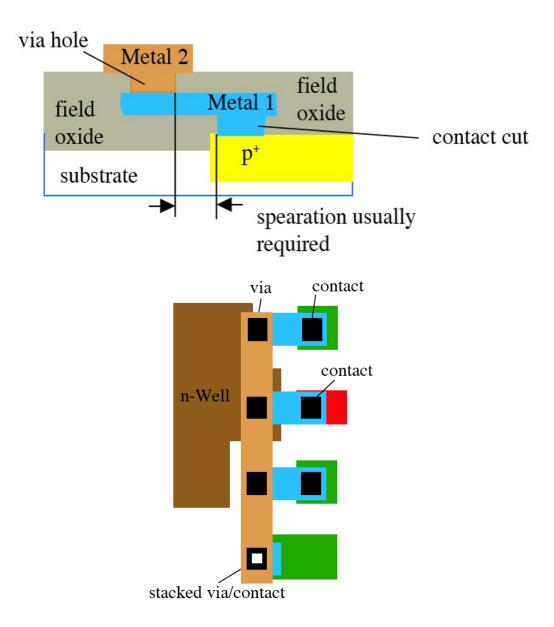

## **Contacts and Vias in CMOS Fabrication**

# MOSIS (MOS Implementation) layout design rules

| Rule num   | ber Description                               | <i>ä</i> | $\lambda$ -Rule |

|------------|-----------------------------------------------|----------|-----------------|

| . 3        | Active area rules                             |          |                 |

| R1         | Minimum active area width                     |          | 3λ              |

| R2         | Minimum active area spacing                   |          | 3λ              |

|            | Polysilicon rules                             | 672      |                 |

| R3         | Minimum poly width                            |          | 2λ              |

| R4 .       | Minimum poly spacing                          |          | 2λ              |

| R5         | Minimum gate extension of poly over active    |          | 2λ              |

| R6         | Minimum poly-active edge spacing              |          | 1λ              |

|            | (poly outside active area)                    |          |                 |

| R7         | Minimum poly-active edge spacing              |          | 3λ              |

|            | (poly inside active area)                     |          |                 |

|            | Metal rules                                   |          |                 |

| <b>R</b> 8 | Minimum metal width                           |          | 3λ              |

| R9         | Minimum metal spacing                         |          | 3λ              |

|            | Contact rules                                 | 25       |                 |

| R10        | Poly contact size                             |          | 2λ              |

| R11        | Minimum poly contact spacing                  |          | 2λ              |

| R12        | Minimum poly contact to poly edge spacing     |          | 1λ              |

| R13        | Minimum poly contact to metal edge spacing    |          | 1λ              |

| R14        | Minimum poly contact to active edge spacing   |          | 3λ              |

| R15        | Active contact size                           |          | 2λ              |

| R16        | Minimum active contact spacing                |          | 2λ              |

|            | (on the same active region)                   |          |                 |

| R17        | Minimum active contact to active edge spacing | 21       | 1λ              |

| R18        | Minimum active contact to metal edge spacing  |          | 1λ              |

| R19        | Minimum active contact to poly edge spacing   |          | 3λ              |

| R20        | Minimum active contact spacing                |          | 6λ              |

|            | (on different active regions)                 |          |                 |

# MOSIS (MOS Implementation) layout design rules

| Rule number | Description                                                     | $\lambda$ -Rule | R9            |

|-------------|-----------------------------------------------------------------|-----------------|---------------|

| 2 ji        | Active area rules                                               |                 | R12           |

| R1          | Minimum active area width                                       | 3λ              |               |

| R2          | Minimum active area spacing                                     | 3λ              |               |

|             |                                                                 | (20) III        |               |

|             | Polysilicon rules                                               |                 |               |

|             |                                                                 |                 |               |

| R3          | Minimum poly width                                              | 2λ              | R10 R1 R2 R20 |

| R4 .        | Minimum poly spacing                                            | 2λ              |               |

| R5          | Minimum gate extension of poly over active                      | 2λ              | B13 .         |

| R6          | Minimum poly-active edge spacing                                | 1λ              | R5            |

|             | (poly outside active area)                                      |                 | R19           |

| R7          | Minimum poly-active edge spacing                                | 3λ              |               |

|             | (poly inside active area)                                       |                 |               |

|             | Metal rules                                                     |                 | R7 R7         |

| R8          | Minimum metal width                                             | 3λ              |               |

| R9          | Minimum metal spacing                                           | 3λ              | R3            |

|             |                                                                 |                 | R8            |

|             | Contact rules                                                   | 20              |               |

|             |                                                                 |                 |               |

| R10         | Poly contact size                                               | 2λ              |               |

| R11         | Minimum poly contact spacing                                    | 2λ              |               |

| R12         | Minimum poly contact to poly edge spacing                       | 1λ              |               |

| R13         | Minimum poly contact to metal edge spacing                      | 1λ              |               |

| R14         | Minimum poly contact to active edge spacing                     | 3λ              |               |

| 11 Paris    | 11                                                              | 200 D           | Active area   |

| R15         | Active contact size                                             | 2λ              |               |

| R16         | Minimum active contact spacing                                  | 2λ              | Polysilicon   |

|             | (on the same active region)                                     |                 |               |

| R17         | Minimum active contact to active edge spacing                   | 1λ              |               |

| R18         | Minimum active contact to metal edge spacing                    | 1λ              | Contact       |

| R19         | Minimum active contact to poly edge spacing                     | 32              |               |

| R20         |                                                                 | 0A              | Metal         |

| R20         | Minimum active contact spacing<br>(on different active regions) | 6λ              | Metal         |

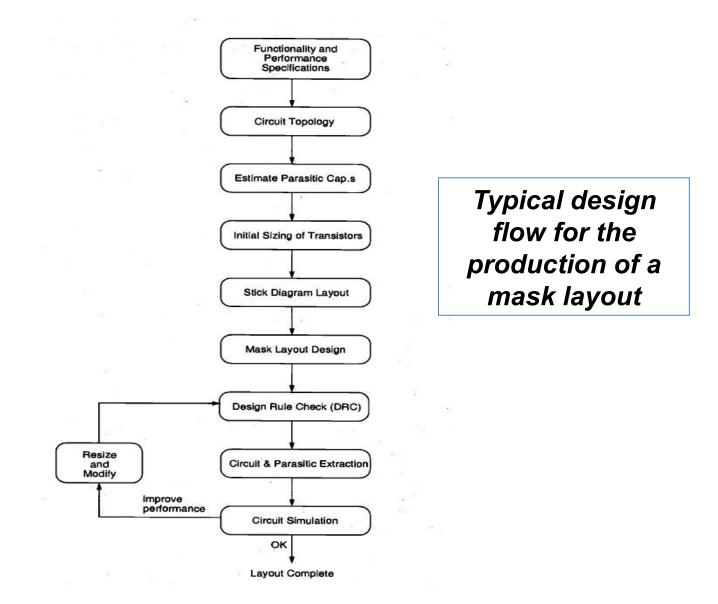

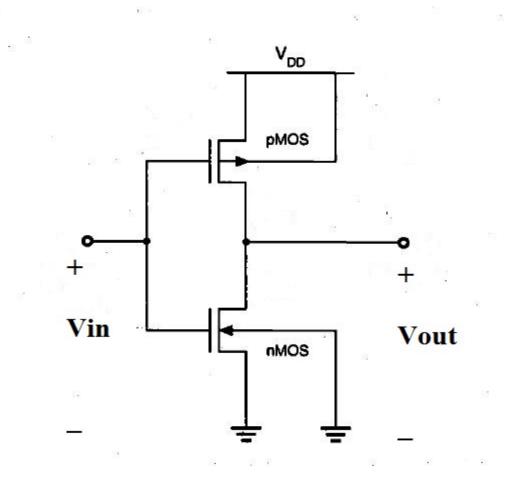

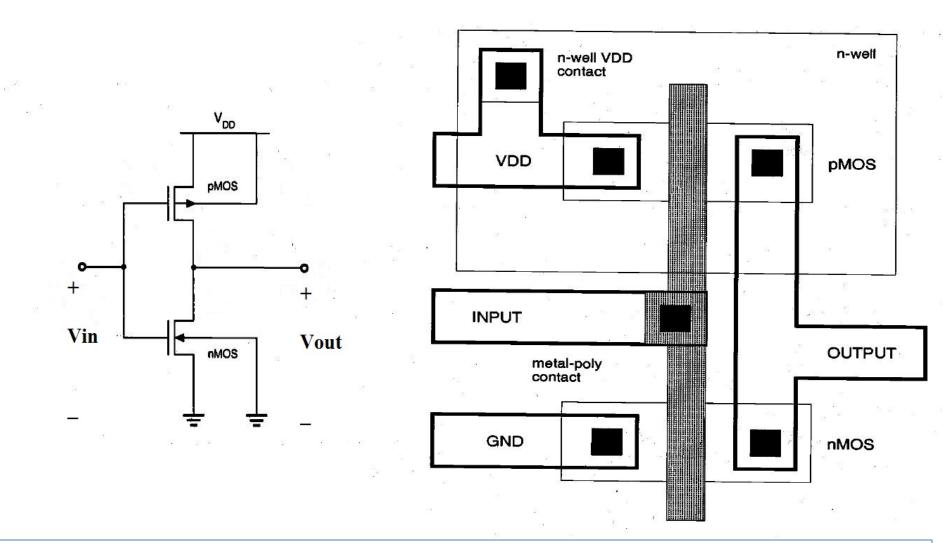

CMOS inverter

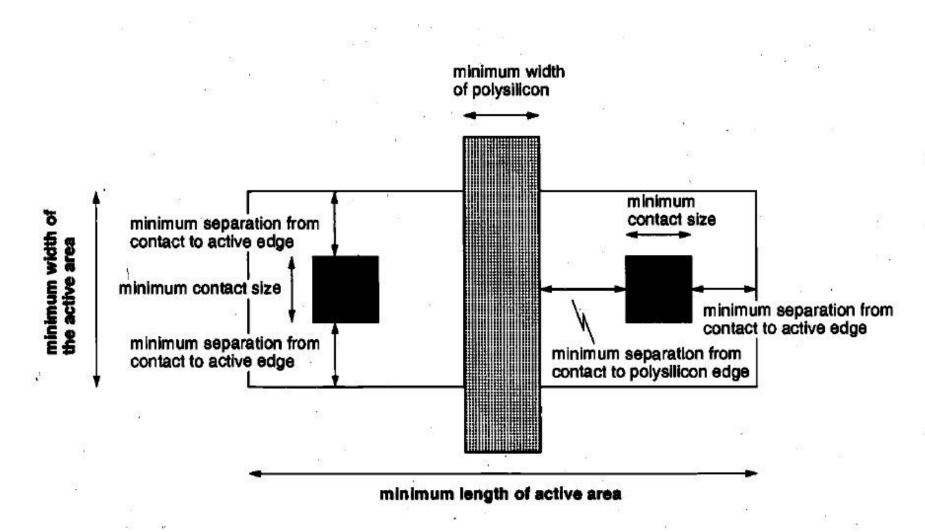

Design rules which determine the dimensions of a min size transistor

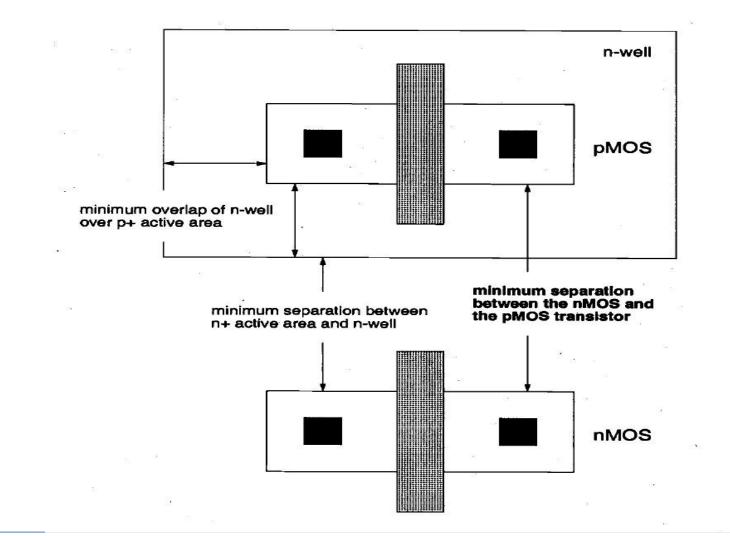

Design rules which determine the separation between nMOS and pMOS transistor

Complete mask layout of the CMOS inverter

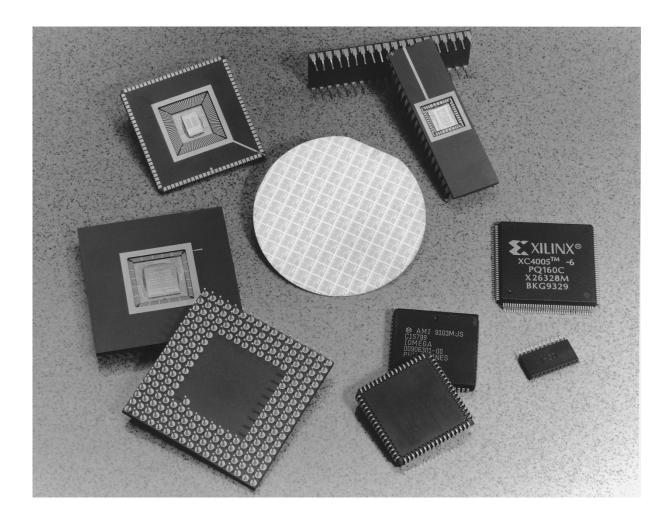

# Packaging Requirements

- Electrical: Low parasitics

- Mechanical: Reliable and robust

- Thermal: Efficient heat removal

- Economical: Cheap

## **Bonding Techniques**

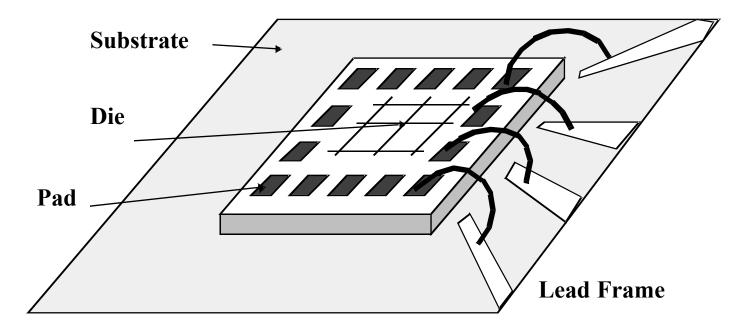

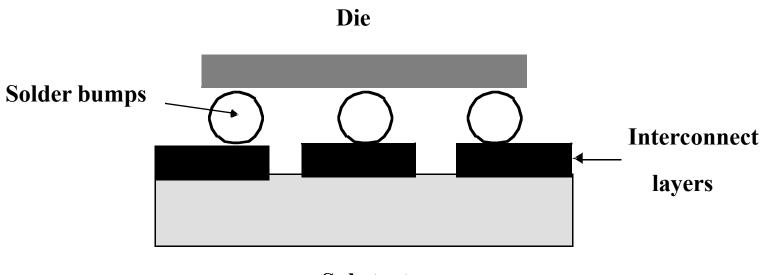

#### **Wire Bonding**

## **Flip-Chip Bonding**

**Substrate**

### Package Types

### **Package Parameters**

| Package Type           | Capacitance<br>(pF) | Inductance<br>(nH) |

|------------------------|---------------------|--------------------|

| 68 Pin Plastic DIP     | 4                   | 35                 |

| 68 Pin Ceramic DIP     | 7                   | 20                 |

| 256 Pin Pin Grid Array | 5                   | 15                 |

| Wire Bond              | 1                   | 1                  |

| Solder Bump            | 0.5                 | 0.1                |

Typical Capacitances and Inductances of Various Package and Bonding Styles (from [Sze83])