# ESE 566A Modern System-on-Chip Design

## Xuan 'Silvia' Zhang Washington University in St. Louis

http://classes.engineering.wustl.edu/ese566/

**Course Overview**

Objectives

Motivations

Structure

Logistics

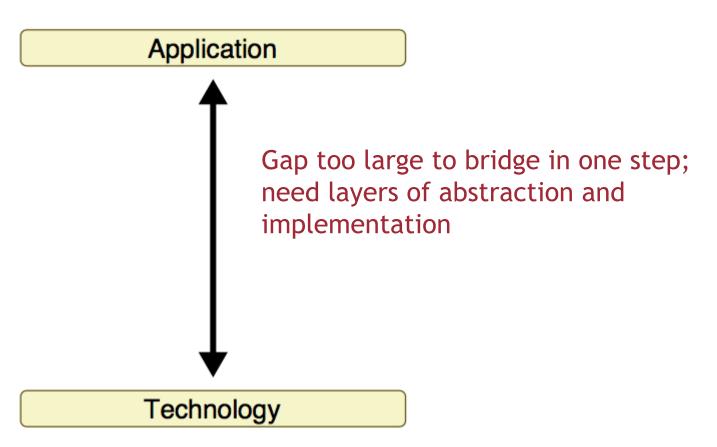

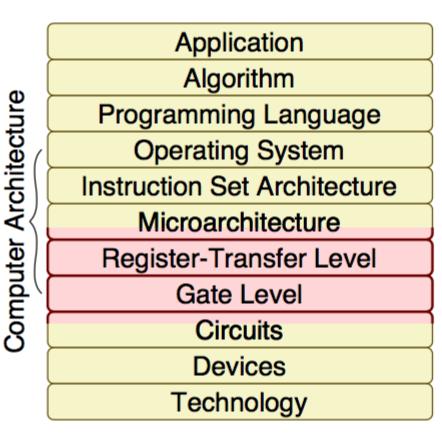

#### **Computer Engineering Stack**

- Bridge application and technology

- examples

- app: navigation (North), tech: magnetic compass

- app: face recognition, tech: charge-coupled device (CCD)

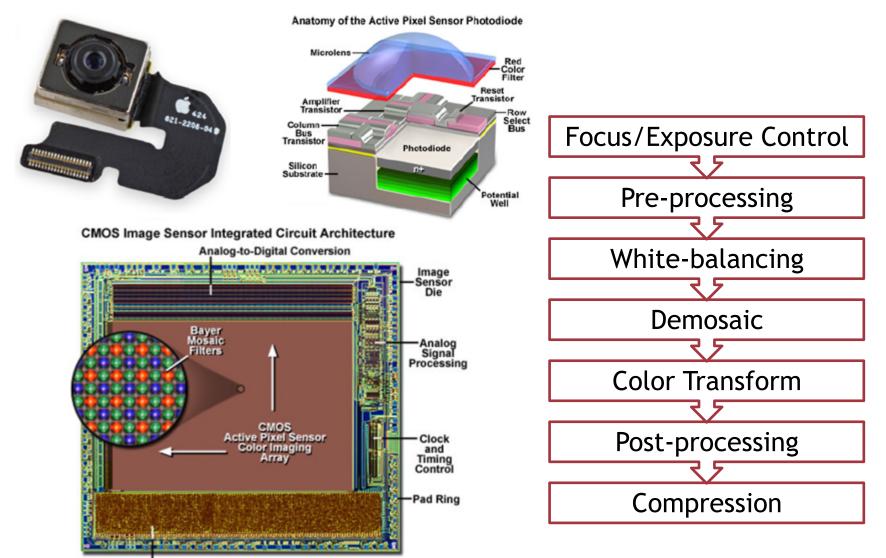

#### Interface to the Physical World: The camera

Digital Logic (Interface, Timing, Processing, Output)

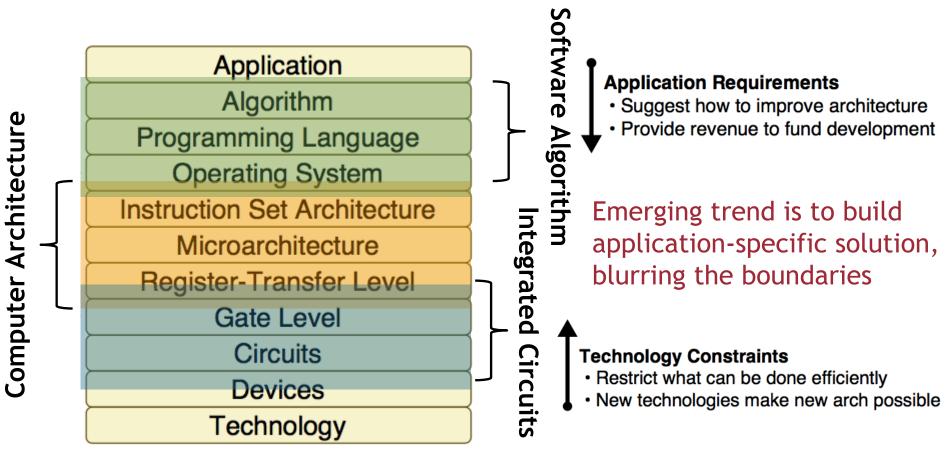

#### **Computer Engineering Stack**

- Circuit, Architecture, and Algorithm

- traditional division

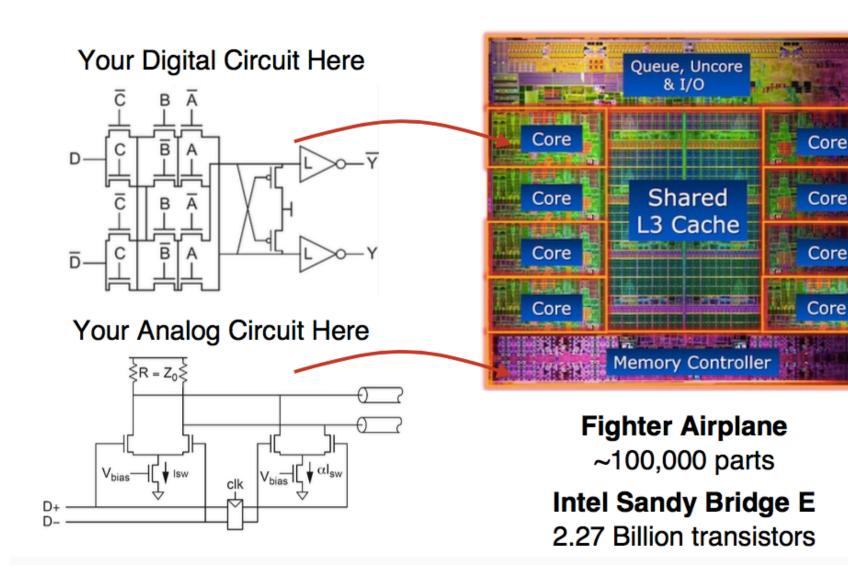

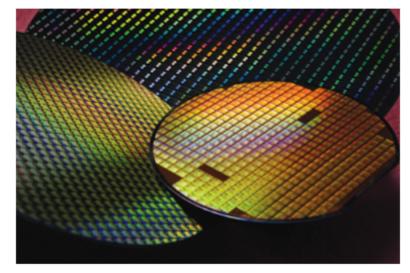

#### What is a System-on-Chip (SoC)?

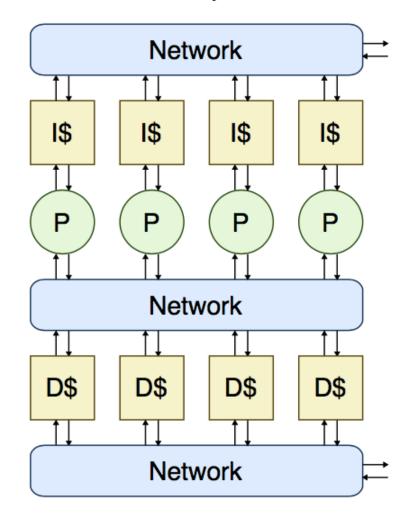

- Contain general-purpose processor

- but also other computing units

- Designed for specific application

- Small, low power, portable

- Unique architecture

- core, memory, accelerators, peripherals

- Combine digital, analog, mixed-signal

- Power management circuits

- Timing source

- Cost constrained

SoC is the perfect place where circuit, architecture, and algorithm meet; use it as a teaching example.

#### **Course Objectives**

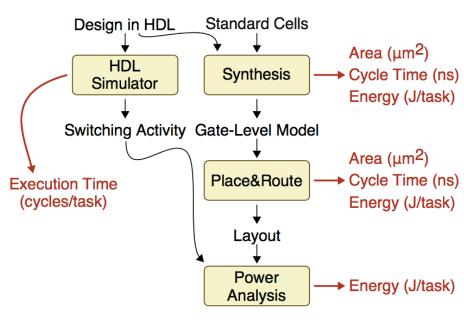

- Understand basic IC technology and design flow

- CMOS device and circuits

- language: Verilog

- tools: Synopsys, Cadence

- process: design, simulation, synthesis, verification, test

- principles: performance, power, other considerations

- Understand key architecture concepts and metrics

- processor, memory, network

- speed, power/energy, complexity/chip area

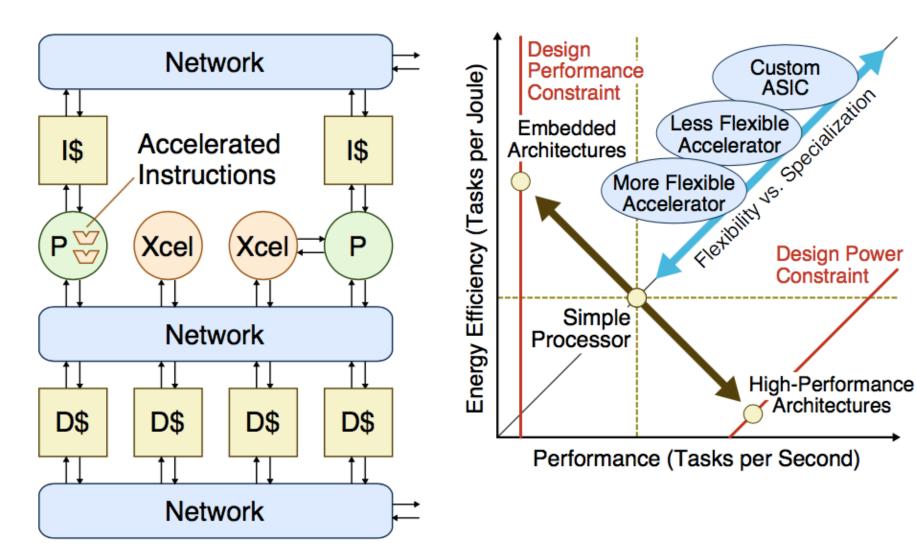

- Introduce advanced tools for future system design

- high-level synthesis, hardware acceleration

**Course Overview**

Objectives

Motivations

Structure

Logistics

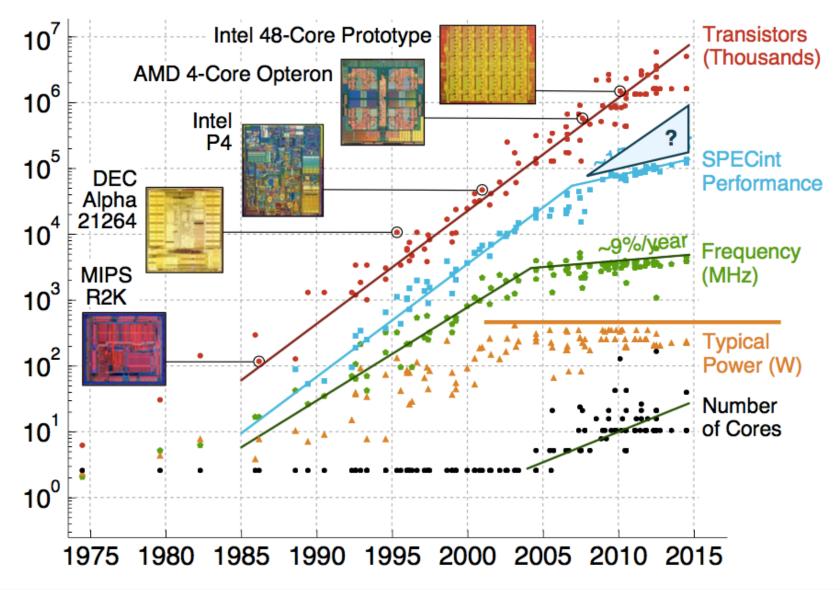

#### **Computer Architecture Research Perspective**

#### **Cross-Layer Interaction is Critical**

Need to quantitatively understand area, cycle time, and energy tradeoffs to create new architectures

10

#### **Circuit Research Perspective**

#### **Cross-Layer Interaction is Critical**

Application Algorithm Computer Architecture Programming Language **Operating System** Instruction Set Architecture Microarchitecture **Register-Transfer Level** Gate Level Circuits Devices Technology

Need to appreciate the system-level context for their subsystems to identify exciting new opportunity

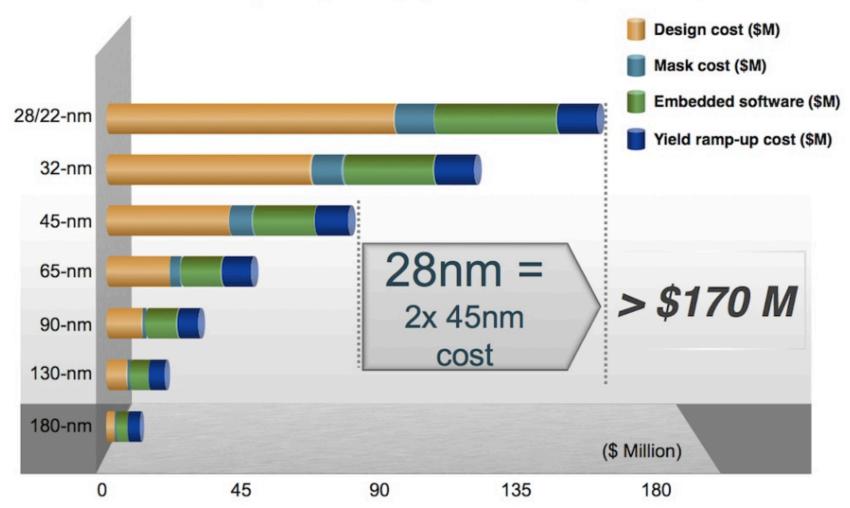

#### **Industry Development Perspective**

Industry at a cross-road

Estimated Chip Design Cost, by Process Node, Worldwide, 2011

### Case Study: Internet-of-Things (IoT)

Meet the Nest Thermostat Install & Explore

BUY NOW

## Programs itself. Then pays for itself.

Meet the 3rd gen Nest Learning Thermostat. It's slimmer and sleeker with a bigger, sharper display. And it saves energy. That's the most beautiful part. Watch video •

**BUY NOW**

Get a \$100 rebate from Ameren Missouri >

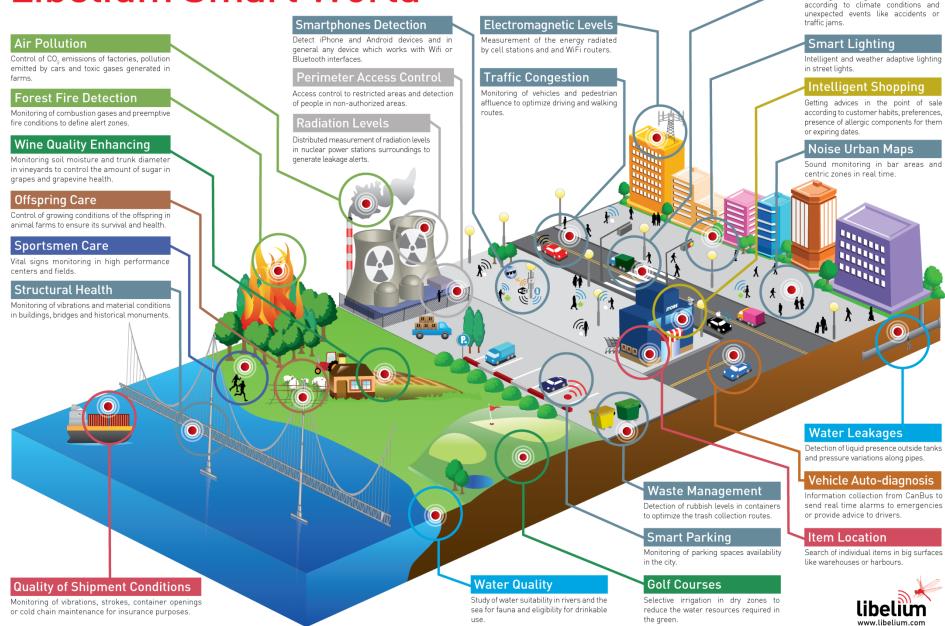

## Libelium Smart World

Smart Roads

Warning messages and diversions

#### Case Study: Deep Learning Hardware

- Artificial Intelligence (AI)

- Machine Learning

- a branch of machine learning

- deep neural networks (DNN)

- convolutional neural networks (CNN)

- recurrent neural networks (RNN)

# Artificial intelligence now fits inside a USB stick

) Everywhere you go, you'll always take the neural network with you )

Aaron Souppouris , @AaronIsSocial 04.28.16 in Robots

Comr

655 Shares

#### Case Study: Deep Learning Hardware

## Nervana Engine delivers deep learning at ludicrous speed!

Nervana is currently developing the Nervana Engine, an application specific integrated circuit (ASIC) that is custom-designed and optimized for deep learning.

Training a deep neural network involves many compute-intensive operations, including matrix multiplication of tensors and convolution. Graphics processing units (GPUs) are more well-suited to these operations than CPUs since GPUs were originally designed for video games in which the movement of on-screen objects is governed by

Discoverin

vectors and linear algebra. As a result, GPUs have become the go-to computing platform for deep learning. But there is much room for improvement — because the numeric precision, control logic, caches, and other architectural elements of GPUs were optimized for video games, not deep learning.

#### **Industry Development Perspective**

• Incumbent players and new comers

Objectives

Motivations

Structure

Logistics

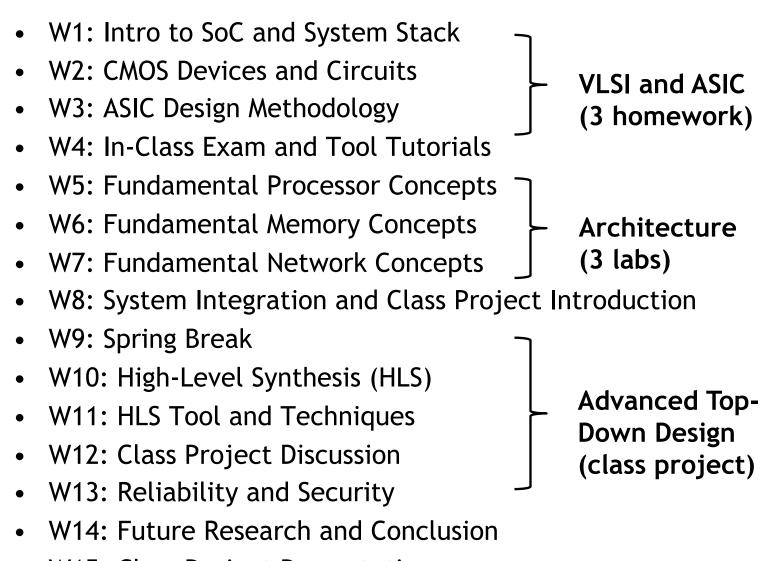

#### Tentative Schedule

#### Labs: Deepen Understanding of Design and System

#### Lab 1: Design Flow

Lab 2: Multiplier

#### Lab 3: Memory Controller

#### **Class Project: Application Specific Accelerator**

Objectives

**Motivations**

Structure

Logistics

#### Instructional Staff (see homepage for contact info, office hours)

Xuan 'Silvia' Zhang (Mon 4-5pm) Dengxue Yan (Thur 3:30-5pm) Yunfei Gu (Tue 3:30-5pm)

#### Prerequisites

- ESE 232: Introduction to Electronic Circuits

- analysis and design of transistors

- semiconductor memory devices

- ESE 260: Introduction to Digital Logic and Computer Design

- combinational and sequential logic

- logic minimization, propagation delays, timing

- Hardware description language (Verilog, VHDL)

- Recommended

- basic computer architecture (CSE 362M)

- basic design flow (ESE 461)

- basic system implementation (CSE 462M)

#### **Course Overview**

- Course homepage:

- http://classes.engineering.wustl.edu/ese566/

- Distribution

- 30%: reading and learning

- 70%: programming, debugging, design iteration

- Course load

- one in-class exam

- 4 homework (one per week)

- 3 labs (one every two weeks)

- one final project (3-person team)

- Philosophy

- learner-directed instruction

#### **Final Project**

- Goal: <u>learn by doing</u>

- Work in teams of 3

- Topic fixed, implementation open-ended

- Release around Week 9 (spring break)

- Optimize design to meet/exceed performance goals

- A custom designed IC chip as the end result

- Evaluation

- Completion of the design flow

- Performance achieved

- Techniques applied

- Proposal, mid-proj report, presentation, final report

#### Grading

- Engagement 5%

- In-Class Exam 10%

- Homework 20%

- Labs 30%

- Class Project 35%

- Policy:

- 90% or above A

- 80% 89% B

- 65% 79% C

- 45% 64% D

- 44% or below F

#### Policies

- Submission

- labs and homework due Monday before lecture

- fixed 3 slip days on homework and 3 slip days on lab

- each team has 4 slip days on class project

- Discussion & Collaboration

- learning through discussion

- help classmates to understand concepts

- sharing code or schematics not-allowed

- Plagiarism

- zero tolerance

- specify sources to avoid confusion

#### Textbook

- Lecture Slides and Notes

- Tutorials

- Documentations

- Recommended Textbook

- "Computer System Design: System-on-Chip" by Michael

J. Flynn and Wayne Luk

- free ebook can be access via WashU lib

#### Is ESE 566A right for you?

- Advanced graduate-level fast-paced;

- 6~8 hours/week load (week1-5);

- 10~12 hours/week load (week6-14);

- lots of coding and debugging for lab and class projects;

- not the class to teach you coding;

- not the class to teach you Verilog;

- you have to work out your own solution.

Next Step After Lec #1

- Enrollment

- decide to enroll or drop, capacity limited

- Piazza

- sign up instruction to follow

- questions relating to class will be directed to Piazza

- Github

- sign up instruction to follow

- all lab and class project submissions on Github

- SEAS account

- design software on LinuxLab

- tutorial to be released.

- Homework 1

- will be posted on class website. due on 1/23 at 2:30pm.

### Questions?

#### Comments?

#### Discussion?

#### Acknowledgement

#### Cornell University, ECE 5745