# Lecture 12 Timing Analysis, Part 1

Xuan 'Silvia' Zhang

Washington University in St. Louis

http://classes.engineering.wustl.edu/ese461/

#### Types of Simulation

- Behavioral simulation

- black box with inputs and outputs

- Functional simulation

- unit-delay simulation; ignore timing

- Static timing analysis

- derive the longest delay path

- Gate-level simulation

- aka. logic simulation; check ASIC timing performance

- logic cell as black box modeled by functions with input signal as variables

- Switch-level simulation

- Transistor or circuit-level simulation

higher level less accurate faster

lower level more accurate slower

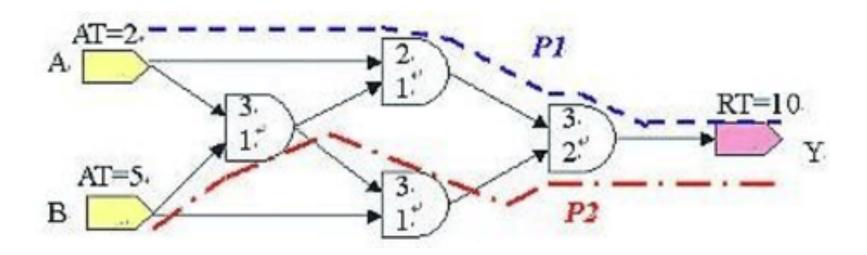

- "What is the longest delay in my circuit?"

- critical path delay

- determines the max clock frequency

- Dynamic analysis

- vector-based simulation

- find the input vector that activates the longest path

- false path example

- Static timing

- worst case analysis

- no consideration of the input vector

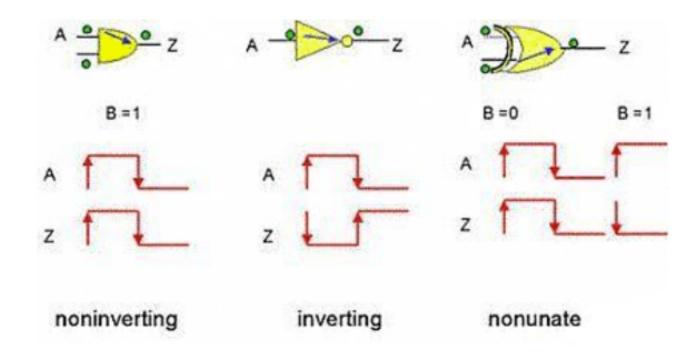

#### **Delay Models**

- Timing vs delay model

- timing model: delay outside the logic cells

- delay model: delay inside the logic cells

- Types of delays

- pin-to-pin: input pin to output pin, excluding interconnect

- pin delay: delay lumped to pin

- net/wire delay: interconnect

- Linear delay model

- prop-ramp delay model

$$t_{PD} = R(C_{out} + C_p) + t_q$$

- standard cell library data book

pin I (input) =

$$0.060$$

pF pin ZN (output) =  $0.038$  pF

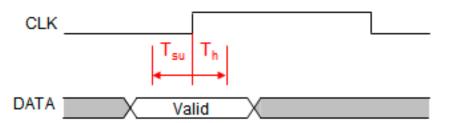

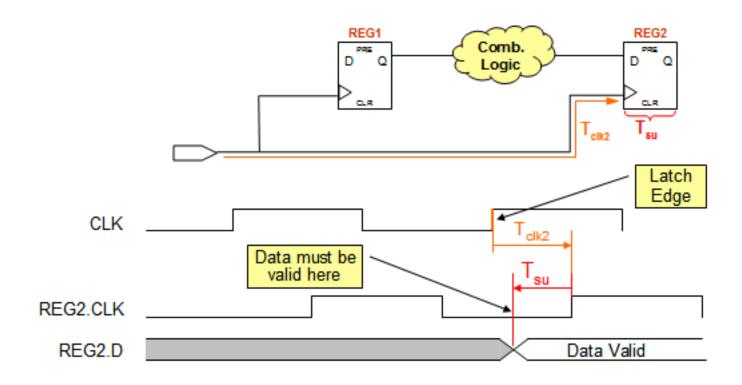

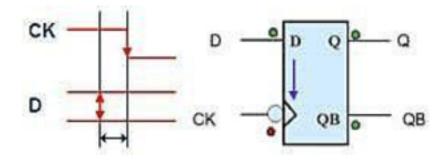

- Setup time

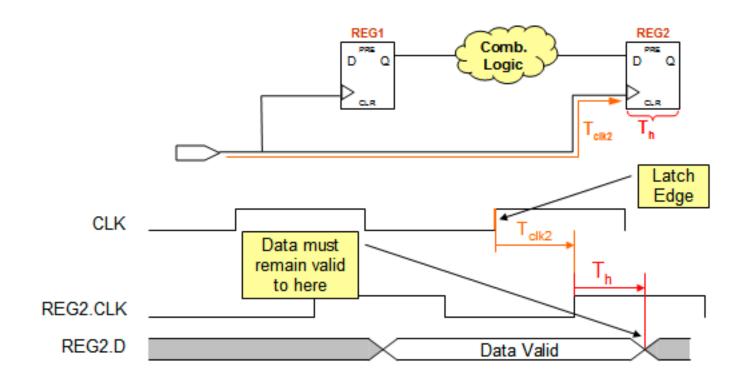

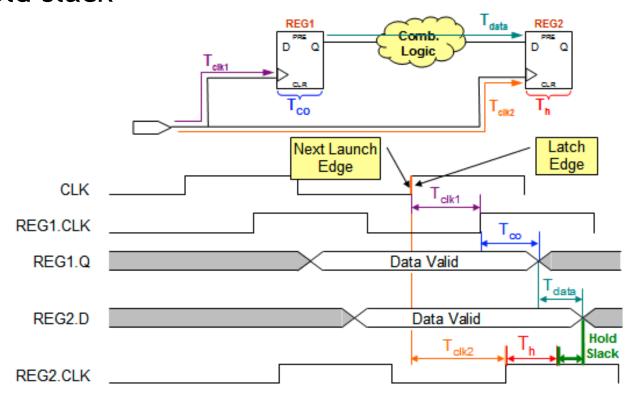

- Hold time

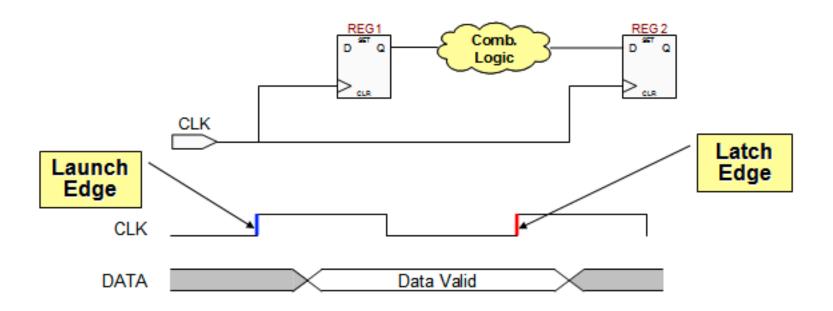

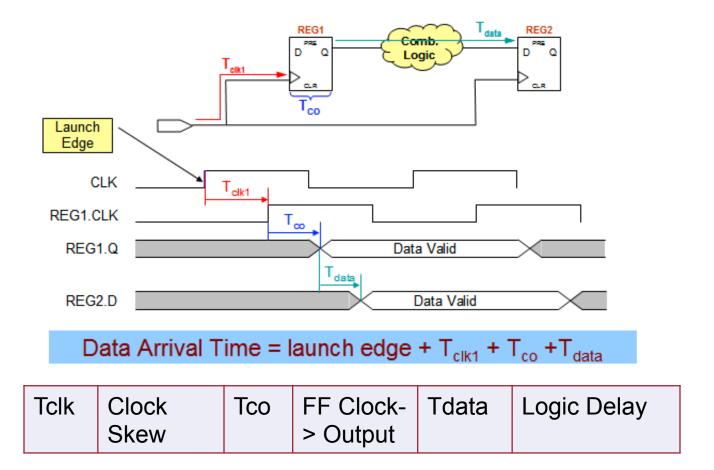

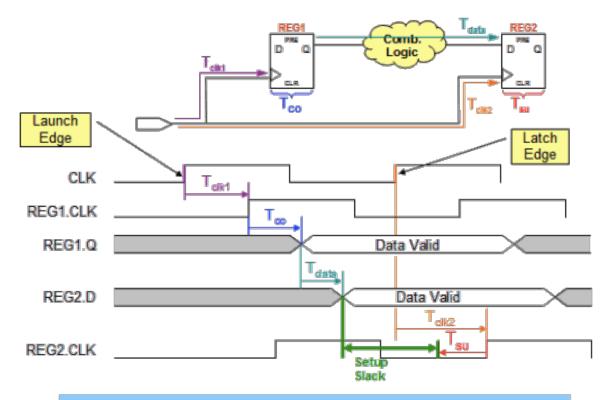

• Launch edge and latch edge

Data arrival time: using launch edge

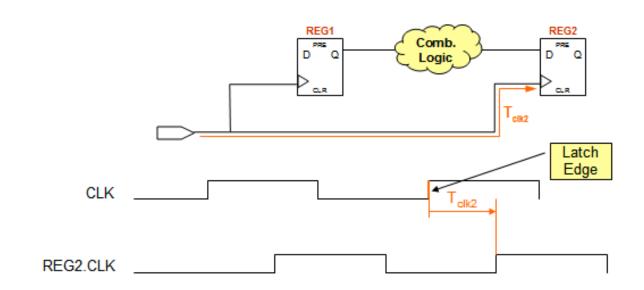

Clock arrival time

Clock Arrival Time = latch edge + T<sub>clk2</sub>

Data required time (setup): latch edge

Data Required Time = Clock Arrival Time - T<sub>su</sub> - Setup Uncertainty

Data required time (hold): next launch = latch

Data Required Time = Clock Arrival Time + T<sub>h</sub> + Hold Uncertainty

Setup slack

Setup Slack = Data Required Time - Data Arrival Time

Positive slack

Timing requirement me

Negative slack Timing requirement not met

#### Hold slack

Hold Slack = Data Arrival Time - Data Required Time

Positive slack Timing requirement me Negative slack

Timing requirement not met

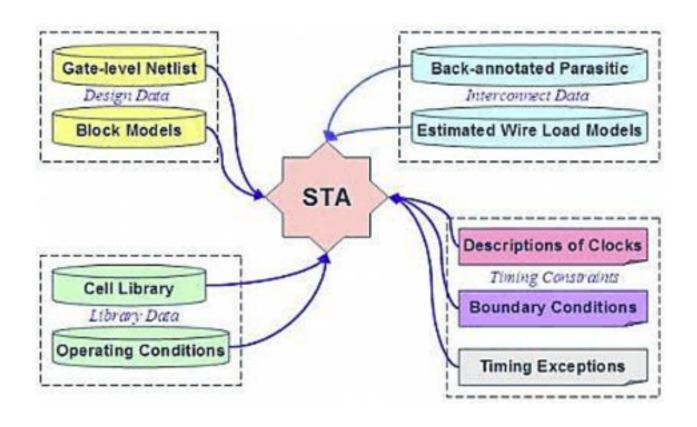

- Timing Model and Timing Constraint

- Arrival Time (AT) and Required Time (RT)

Library Data

#### Timing type

- Combinational Timing (Delay)

- Setup Timing (Check)

- Hold Timing (Check)

- Edge Timing (Delay)

- Present and Clear Timing (Delay)

- Recovery Timing (Check)

- Removal Timing (Check)

- Three State Enable & Disable Timing (Delay)

- Width Timing (Check)

• Combinational Timing (Delay)

• Setup Timing (Check)

Hold Timing (Check)

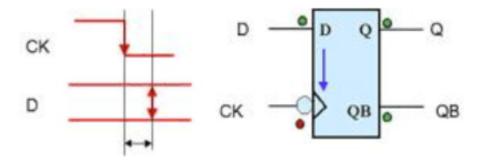

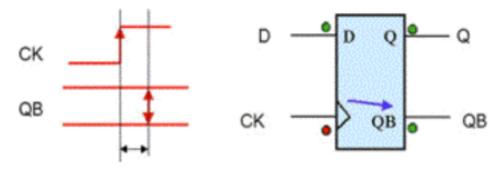

• Edge Timing (Delay)

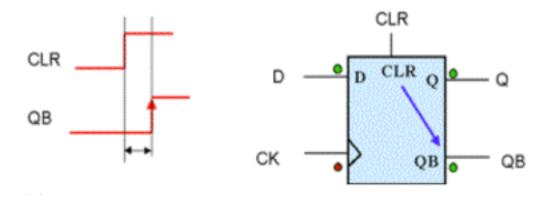

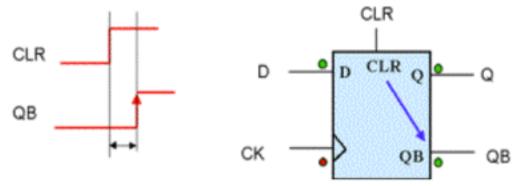

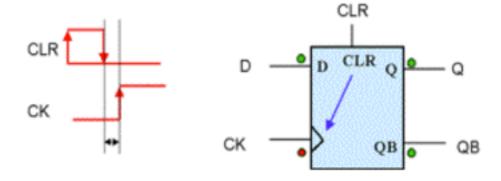

Preset and Clear Timing (Delay)

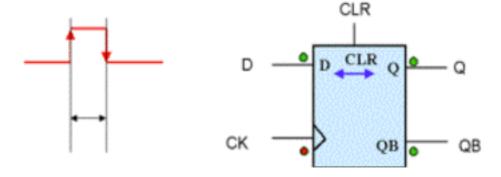

Recovery Timing (Check)

Removal Timing (Check)

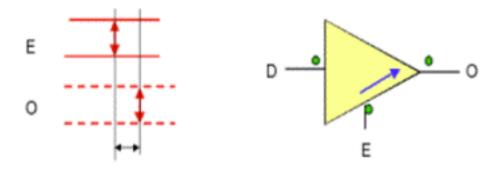

• Three State Enable & Disable Timing (Delay)

• Width Timing (Check)

- Interconnect Delay

- Depends on P&R (Place and Routing)

- Wireload Model: Fan-out

- RC Extraction

- Back-annotate for STA

#### Reference

• Chapter 13 from the ASIC book

Questions?

Comments?

Discussion?